Vorteile des System Power Management Interface (SPMI)

Was ist System Power Management Interface (SPMI)?

Die Komplexitäts- und Leistungsanforderungen von Mobiltelefonen und anderen tragbaren elektronischen Geräten nehmen exponentiell zu. Mit zunehmender Nachfrage nach neuen Funktionen mit hoher Leistung und hoher Datenrate wird die Energieverwaltung auf Systemebene von entscheidender Bedeutung. Der Einsatz fortschrittlicher Energieverwaltungstechniken zur Reduzierung des Stromverbrauchs und zur Verbesserung der Batterielebensdauer ist wichtiger als je zuvor.

Die System Power Management-Schnittstelle (SPMI) ist eine MIPI-Standardschnittstelle, die den integrierten Power Controller (PC) eines System-on-Chip-Prozessorsystems (SoC) mit einem oder mehreren PMIC-Spannungsregelungssystemen (Power Management Integrated Circuits) verbindet. Mit SPMI können Systeme die Versorgungs- und Substratvorspannungen der Spannungsbereiche innerhalb des SoC mithilfe eines einzelnen SPMI-Busses dynamisch anpassen.

Um den Stromverbrauch digitaler Prozessoren in tragbaren elektronischen Geräten zu minimieren, verwenden System- und IC-Entwickler fortschrittliche Energieverwaltungstechniken.

Fortgeschrittene Hardware- und Softwaretechniken werden verwendet, um:

- Genaue Überwachung und Steuerung des Prozessorleistungsniveaus, das für eine bestimmte Arbeitslast oder Anwendung erforderlich ist.

- Steuern verschiedener Versorgungsspannungen basierend auf dem Leistungsniveau Die schnelle Bereitstellung solcher fortschrittlicher Energieverwaltungstechniken erfordert eine Standardisierung der Schnittstelle. Diese SPMI-Spezifikation (System Power Management Interface) befasst sich mit der Standardisierung der Hardwareschnittstelle.

Wie funktioniert SPMI?

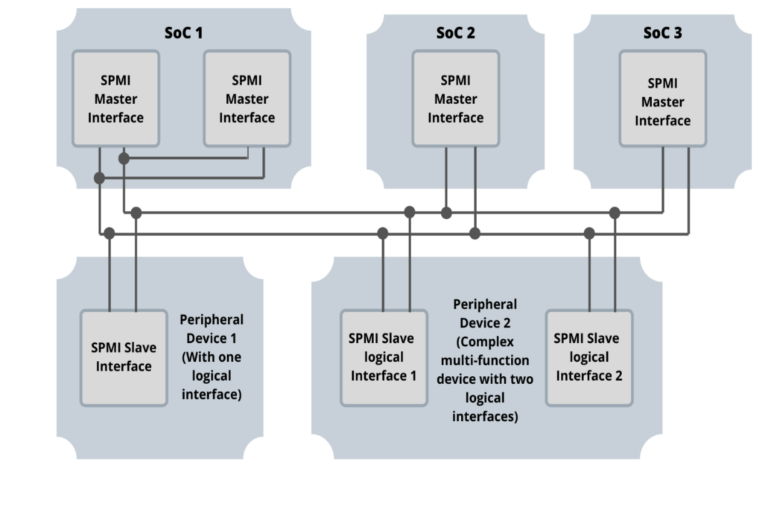

Innerhalb des SoC-PCs werden die SPMI-bezogenen Funktionen als „Master“ bezeichnet. Innerhalb von PMIC werden die SPMI-bezogenen Funktionen als "Slave" bezeichnet. Es können bis zu 4 Master und bis zu 16 Slaves an System angeschlossen sein. Mehrere Master und Slaves können sich auf einem einzelnen IC, auf mehreren ICs oder einer beliebigen Kombination aus beiden befinden.

Welche Vorteile bietet SPMI?

SPMI bietet eine breite Palette von Anwendungen, die auf Branchen verteilt sind, die ein besseres Energiemanagement benötigen. SPMI wird in Smartphones, Wearables und anderen tragbaren elektronischen Geräten verwendet. Smartphones und Wearables verwenden SPMI zur Steuerung der Leistung von Sensoren. High-End-Smartphones haben bereits mehrere Geräte im Design und können bis zu 20 Signalleitungen benötigen. Jeder dieser Stifte mit unabhängigen Stromversorgungsstiften kann Probleme verursachen. In ähnlicher Weise würden die meisten tragbaren elektronischen Geräte eine Energieverwaltungsschnittstelle benötigen, um den Energieverbrauch zu optimieren und die Anzahl der Pins zu verringern. Dies erfordert für die standardisierte erweiterte Energieverwaltungsschnittstelle.

Welche Funktionen bietet SPMI?

SPMI ist eine serielle Zweidrahtschnittstelle für die erweiterte Energieverwaltung, die den integrierten Leistungsregler des SoC-Prozessorsystems mit einem oder mehreren Spannungsregelungssystemen für integrierte Leistungsverwaltungsschaltungen (PMIC) verbindet. Die bidirektionalen zwei Linien repräsentieren SDATA & SCLK. SDATA ist eine bidirektionale Datenleitung und der SCLK wird vom Master gesteuert.

Das SPMI-Protokoll verfügt über die folgenden Funktionen

- Bus Arbitration ist der Prozess, bei dem der Bus einem Master oder einem anforderungsfähigen Slave unter den Geräten zugewiesen werden soll, die gleichzeitig das Senden einer Befehlssequenz auf dem Bus anfordern können.

- Master-Verbindung und -Trennung - Ein Prozess, bei dem ein Master eine Verbindung zu einem initialisierten oder nicht initialisierten SPMI-Bus herstellen und von diesem trennen kann

- Vom Slave initiierte Kommunikation - Ein Prozess für einen Request Capable Slave (RCS), um die Kommunikation mit dem Master oder anderen Slaves zu initiieren.

- Es gibt zwei definierte SPMI-Geräteklassen:

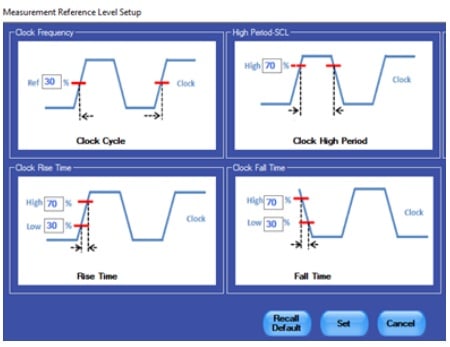

- High-Speed (HS): 32 kHz bis 26 MHz mit einer Last von bis zu 50 pF

- Niedrige Geschwindigkeit (LS): 32 kHz bis 15 MHz bei einer Last von bis zu 50 pF

- ACK / NACK für robuste Kommunikation.

SPMI Befehlssequenzen

Die Folgen müssen aus den folgenden fünf Jahren gehören, die der Reihe nach den:

- Bus Arbitration

- Übertragung der Sequenzstartbedingung (SSC)

- Befehl von Frames und ein oder mehrere Datenframes)

- Übertragung von ACK / NACK für Befehlssequenzen.

- Transport eines Busparkzyklus

Die letzten vier Ereignisse SSC, Befehls- / Datenrahmen, ACK / NACK & Busparkzyklus bilden zusammen die Befehlssequenz. Die SPMI-Spezifikation heißt alle Befehlssequenzen auf der Schnittstelle unter behördlichen Bits.

Die Sequenzstartbedingung muss eine möglicheige Bedingung für den Bus sein, die durch eine ansteigende Flanke von einer abfallenden Flanke an eine SDATA-Verwaltung, eine SCLK auf eine logisch verbundene Pegel bleibt. Der SSC wird von einem Sklaven oder Meister verwendet, um den Start einer Befehlssequenz zu beziehen. SDATA wird durch den Bus - Hauptbesitzer auf einen logischen Pegel eines für einen SCLK genommenen Zeitraum, dann auf den logischen 0 - Pegel für einen SCLK int Periode, gehört der SCLK auf logischen Nullstand.

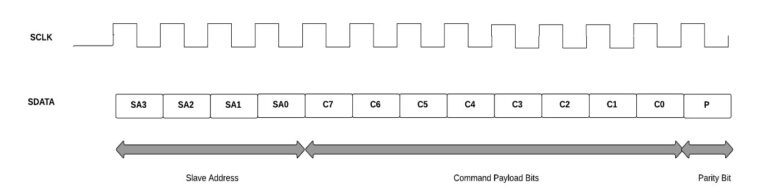

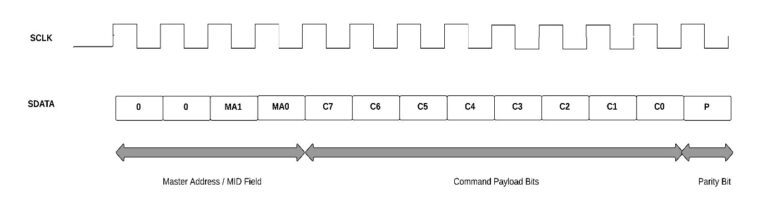

Der Befehlsrahmen besteht aus 13 Bits mit einem 4-Bit-Adressfeld, einem 8-Bit-Befehlsfeld und einem eigenen Paritätsbit.

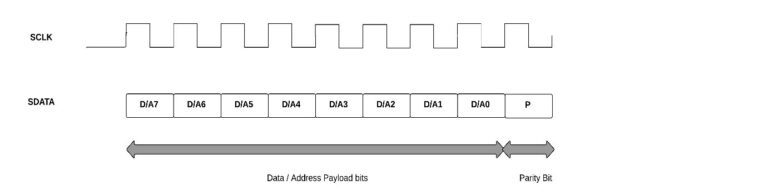

Daten- und Adressrahmen bestehen aus 9 Bits mit 8 Bits Daten oder Adresse und einem einzelnen Paritätsbit.

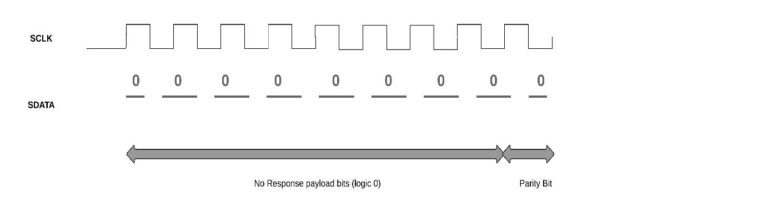

Kein Antwortrahmen mit einer Länge von 9 Bit, wenn es sich um einen Datenrahmen handelt, oder 13 Bit, wenn es sich um einen Befehlsrahmen handelt.

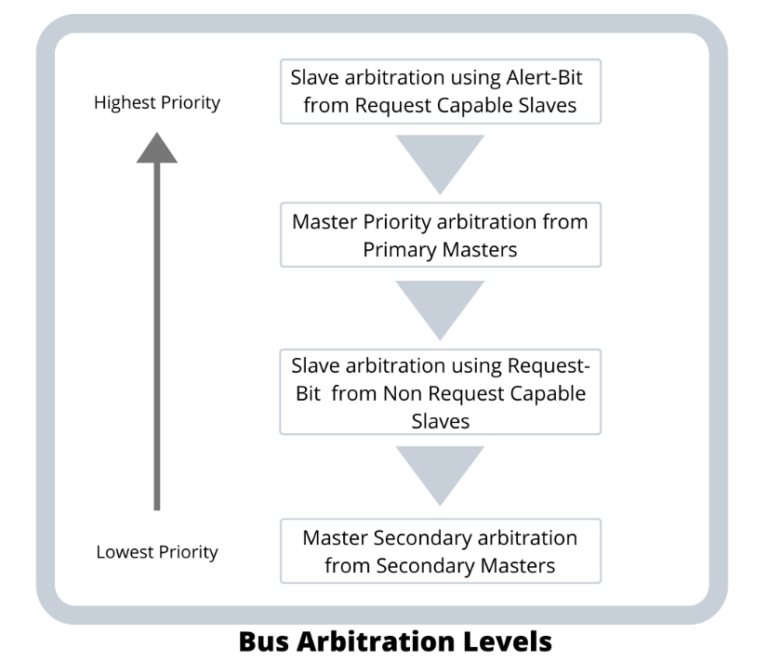

SPMI Bus Arbitrierung

Die Bus-Arbitrierung wird verwendet, um den Zugriff auf den Bus für Master / s oder Slave / s zu bestimmen. Der Busbesitzer-Master überwacht das Schiedsverfahren und bestimmt, wer Zugriff auf den Bus erhält. Die verschiedenen Bus-Arbitrierungsstufen werden nach der Arbitrierungsanforderung in der in der folgenden Abbildung gezeigten Reihenfolge angezeigt.

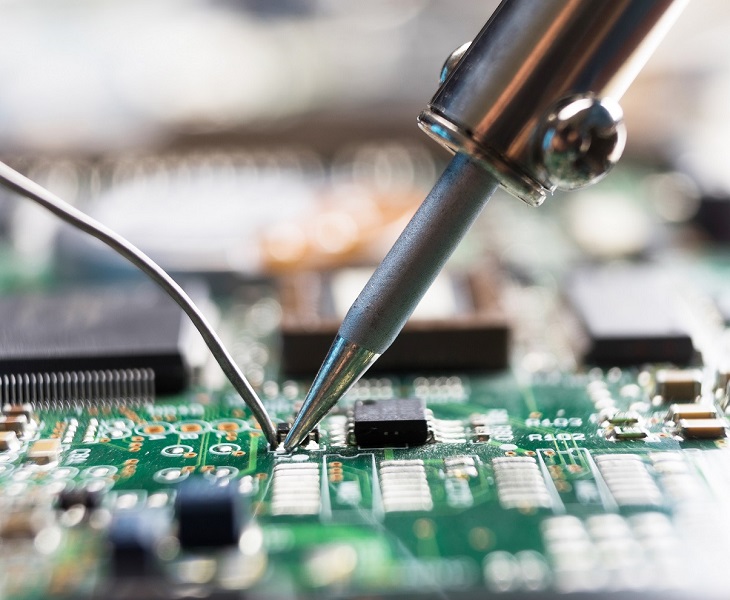

Testen des SPMI-Protokolls

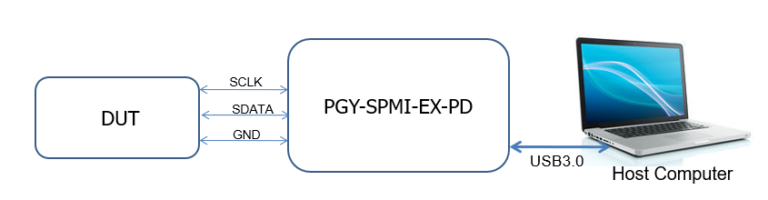

Der typische Testaufbau zum Testen von Master oder Slave ist wie folgt. SPMI DUT kann ein SPMI-Primärmaster, ein Sekundärmaster, ein anforderungsfähiger Slave oder ein nicht anforderungsfähiger Slave sein. Die auf dem Host-Computer ausgeführte Software ermöglicht es dem Benutzer, das Gerät je nach Anforderung im Prüfling entweder als Master oder als Slave zu konfigurieren, indem er die entsprechende Auswahl auswählt.

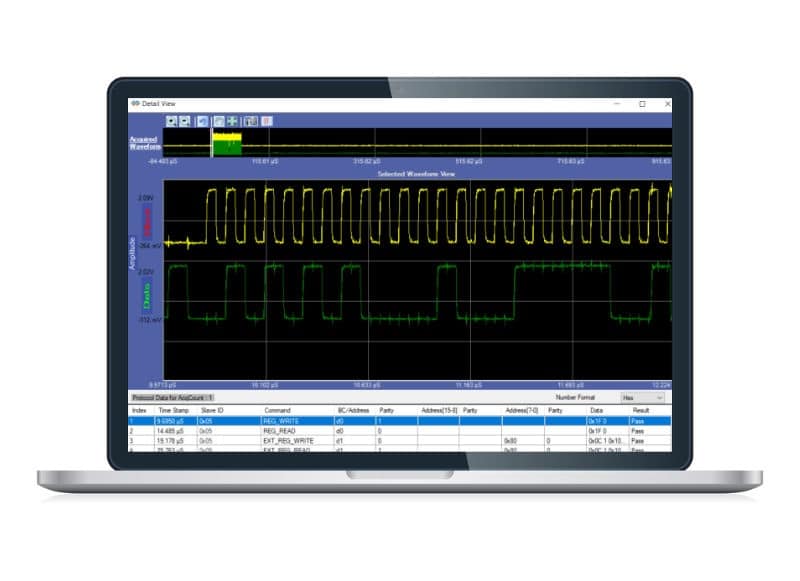

SPMI Protocol Analyzer

PGY-SPMI-EX-PD ist das führende Instrument, mit dem Konstrukteure und Testingenieure die SPMI-Konstruktionen auf ihre Spezifikationen testen können, indem sie PGY-SPMI-EX-ED als Master / Slave konfigurieren und SPMI-Verkehr mit Zeitvariation und Fehlerinjektionsfähigkeit generieren und Decodieren von SPMI-Protokollpaketen.

Preis auf Anfrage

Preis auf Anfrage