Beschreibung

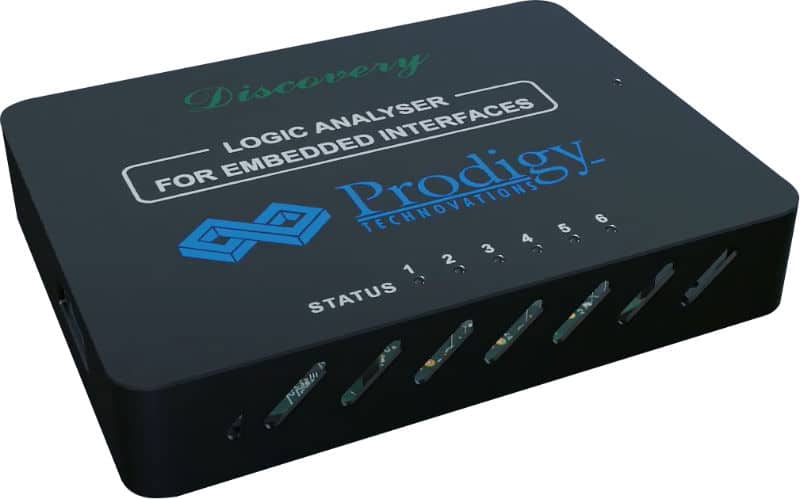

Der Logikanalysator PGY-LA-EMBD ist der branchenweit erste Logikanalysator, der die Fehlersuche bei Timing-Problemen und die gleichzeitige Protokollanalyse von I2C, SPI, UART, I3C, SPMI, CAN/CAN FD und RFFE in Embedded-Designs ermöglicht. So können Sie Probleme auf Schaltkreis- und Systemebene schnell beheben. Dadurch kann man Probleme auf Schaltkreis- und Systemebene schnell debuggen.

Der PGY-LA-EMBD bietet eine asynchrone Datenerfassung mit 1GS/Sekunde (Timing) und eine synchrone Datenerfassung mit 100MHz (Zustand) und ist damit ein ideales Debug-Tool für die Lösung digitaler Designprobleme. Entwickler können nun neben der Analyse von Protokollproblemen auch Setup- und Haltezeitprobleme, Glitches und synchrone Datenaktivitäten schnell analysieren.

Der Logikanalysator ist ein PC-basierter Logikanalysator, der für anspruchsvolle Fachleute entwickelt wurde. Der Discovery Logic Analyzer ist ideal zur Fehlersuche in Embedded-Systemen. Der Logikanalysator hat einen sehr kleinen Formfaktor, so dass er zur Fehlersuche im mobilen Einsatz verwedent werden kann. Die Funktionen zur Protokolldekodierung sind für die Fehlersuche bei Logik- und Protokollproblemen von Embedded-Design-Teams in den Bereichen Konsumgüter, Industrie, Heimautomatisierung, Gesundheit und Bildung konzipiert.

Designer von Embedded Systeme müssen Daten von mehreren Schnittstellen wie 2C, SPI, UART, I3C, SPMI, CAN/CAN FD und RFFE sammeln und verarbeiten, um ein performantes embedded board zu entwicklen. Der PGY-LA-EMBD dekodiert die Busse und zeigt die Protokollaktivität mit Zeitstempelinformationen an. Deswegen ist es ein ideales Instrument für das Debugging von Hardware- und Embedded-Software-Integrationsproblemen und die Optimierung der Softwareleistung.

Mehrere Marker ermöglichen innovative Deltamessungen, die für Entwickler von entscheidender Bedeutung sind. Die Zoomfunktion ermöglicht es dem Benutzer, bestimmte Bereiche des Signals zu betrachten.

Features Logic Analyzer

- 16 Kanäle mit Protokoll- und Logikanalysefunktion.

- 1GS/Sek. Timing (asynchron) Analyse

- 100-MHz-Zustandsanalyse (synchron)

- Gleichzeitige Protokollanalyse von I2C-SPI-UART-I3C-SPMI, CAN/CAN FD, und RFFE.

- Detaillierte Triggerfunktionen: Auto, Muster, Protokollerkennung (I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE) und Timing (Impulsbreite und Verzögerungstrigger).

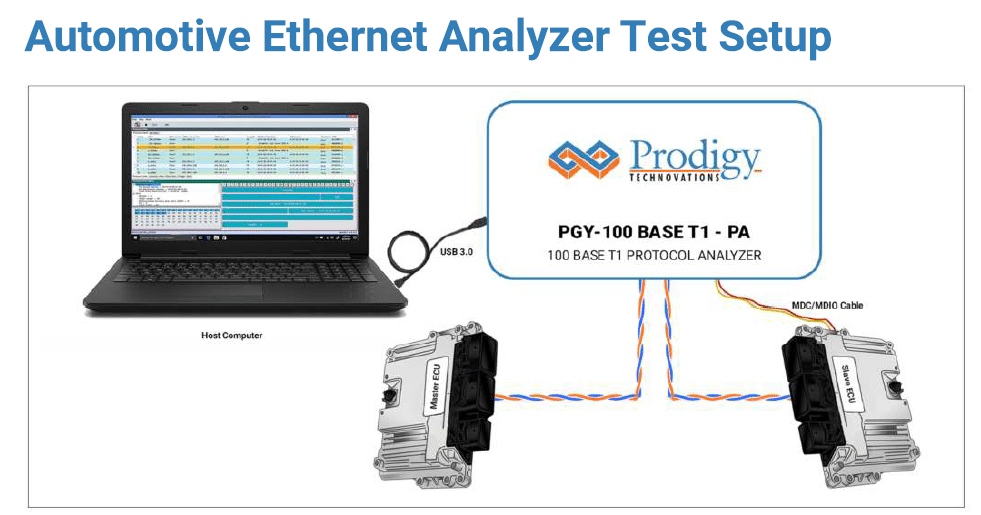

- Intelligentes Streaming von Daten aus dem Protokoll. Analysator an Host-Computer für Langzeiterfassung über USB3.0-Schnittstelle.

- Innovative, einfach zu bedienende grafische Benutzeroberfläche.

- Fehleranalyse des Protokollpakets

- Bietet Timing-, Wellenform-, Auflistungs- und Protokollansichten

- Detaillierte Filterfunktion für protokolldekodierte Daten

- PDF- und CSV-Berichtsformat.

- API-Unterstützung.

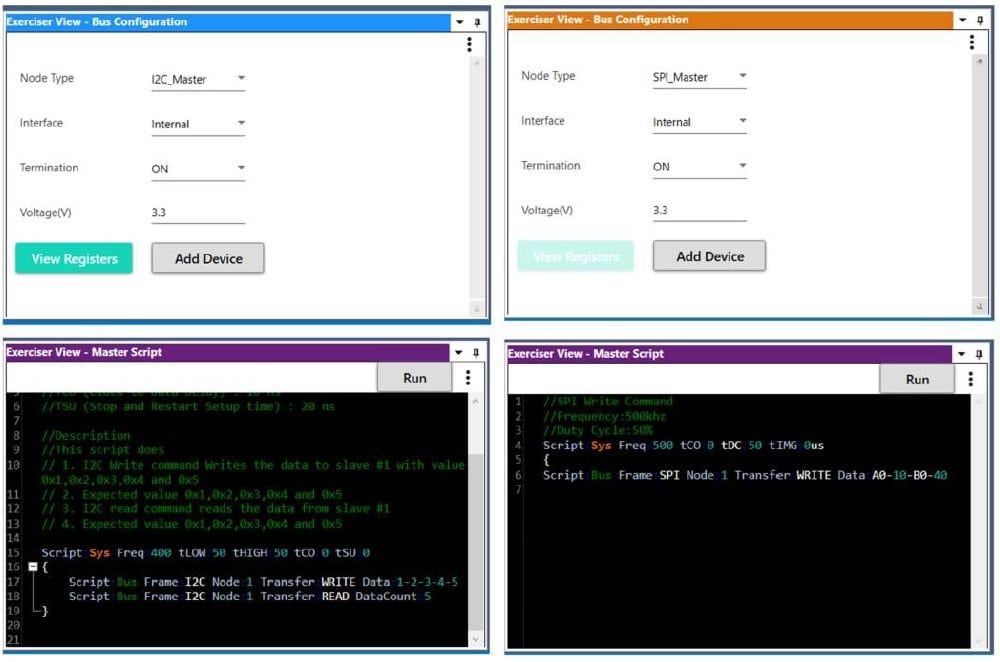

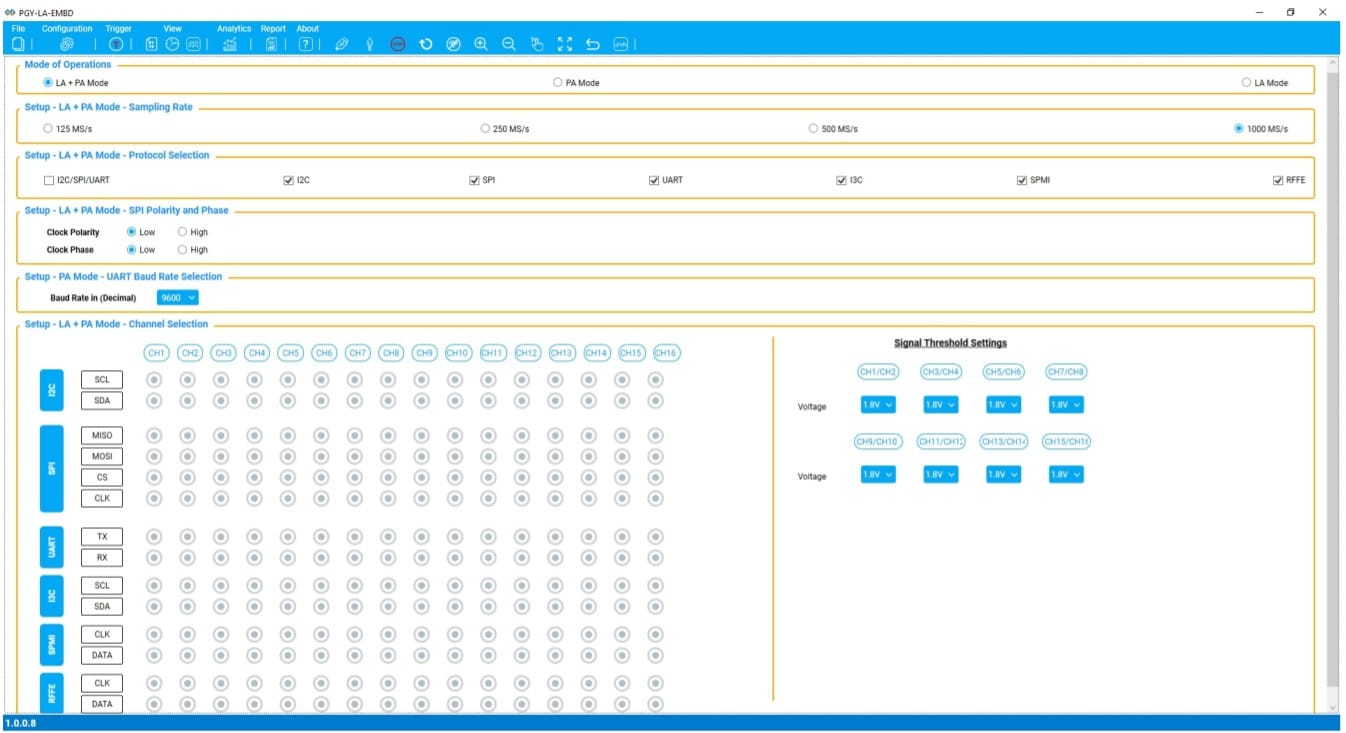

Einfache Konfiguration

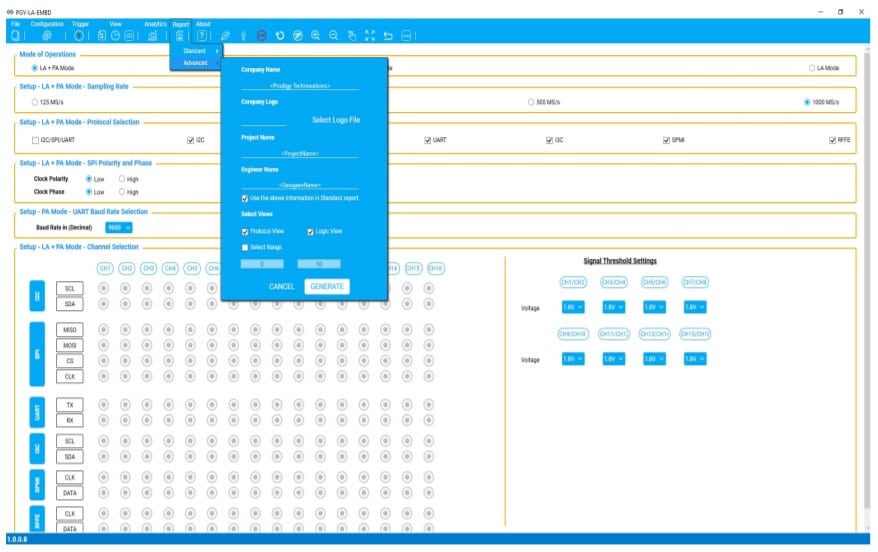

Benutzer können den Logic Analyzer für Embedded-Schnittstellen einfach konfigurieren, indem sie entweder den Modus Logic Analysis (LA) oder den Modus Protocol Analysis (PA) oder einen kombinierten Modus (LA+PA) auswählen. Dies ermöglicht eine schnelle und einfache Konfiguration des Produkts und die Untersuchung komplexer Probleme auf Systemebene entweder in der Logikanalyse (Zustandsanalyse, Timing-Analyse) oder der Protokolldekodierung oder beidem. Die Funktion zum Speichern und Abrufen stellt sicher, dass Entwickler ihre benutzerdefinierten Setup-Details abrufen können.

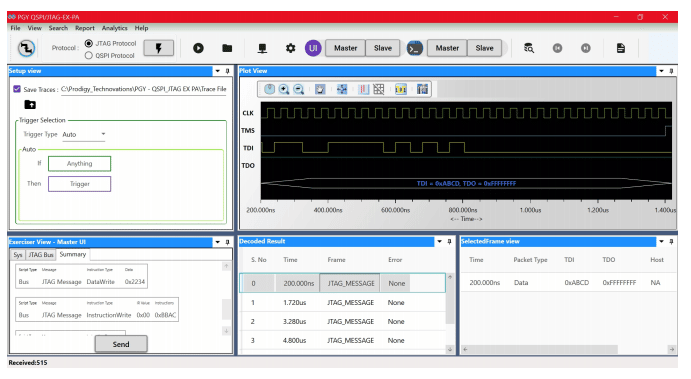

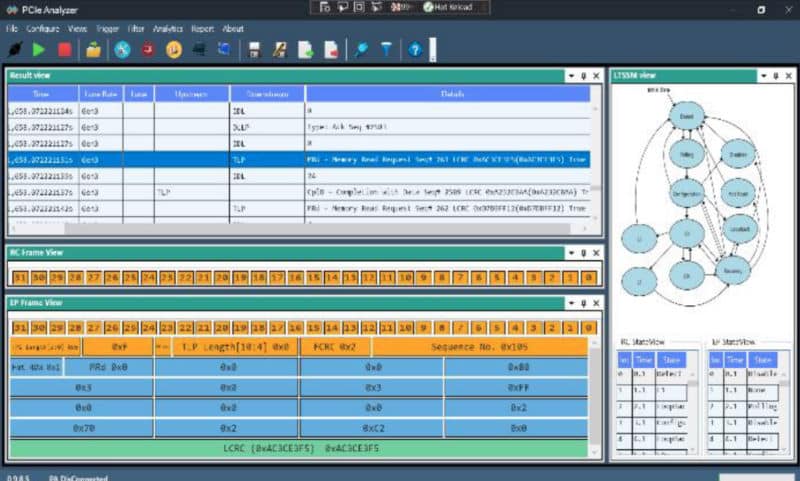

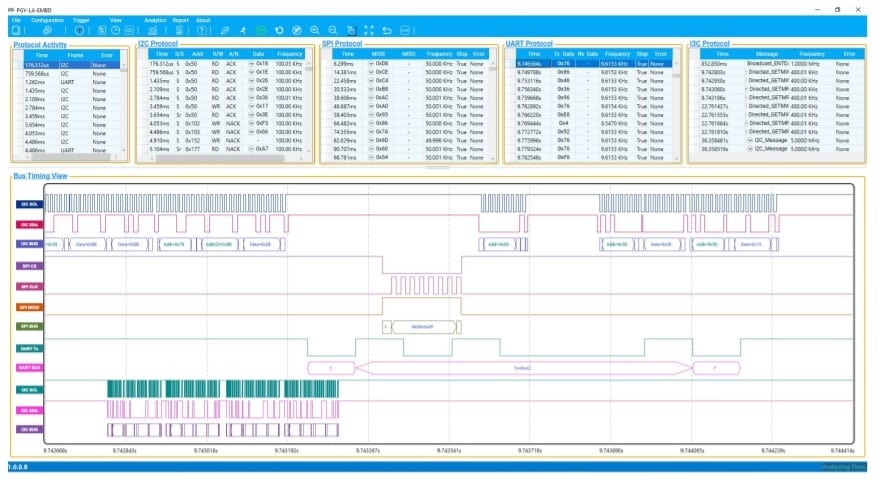

Mehrere Domänenansichten bieten den erforderlichen vollständigen Überblick über den Zustand, das Timing und die Protokollaktivität aller unterstützten Schnittstellen. Benutzer können den Analyzer einfach so einrichten, dass er Timing-, Logik- und Protokolldecodierungsansichten anzeigt, um einen einfachen Einblick in das Design zu ermöglichen. Über das Setup-Menü können verschiedene Trigger-Bedingungen eingestellt werden, um die Timing- und Protokollaktivität bei bestimmten Ereignissen zu erfassen. Die dekodierten Ergebnisse können im Timing-, Logik- und Protokolllistenfenster mit Autokorrelation angezeigt werden. Diese umfassende Ansicht der Informationen macht ihn zu einem der besten in der Branche und bietet eine benutzerfreundliche Lösung zum Debuggen der Protokollaktivität von Embedded-Schnittstellen und zur Analyse von Timing-Problemen. Mehrere Cursor helfen den Entwicklern, die Details ihrer Designleistung zu untersuchen.

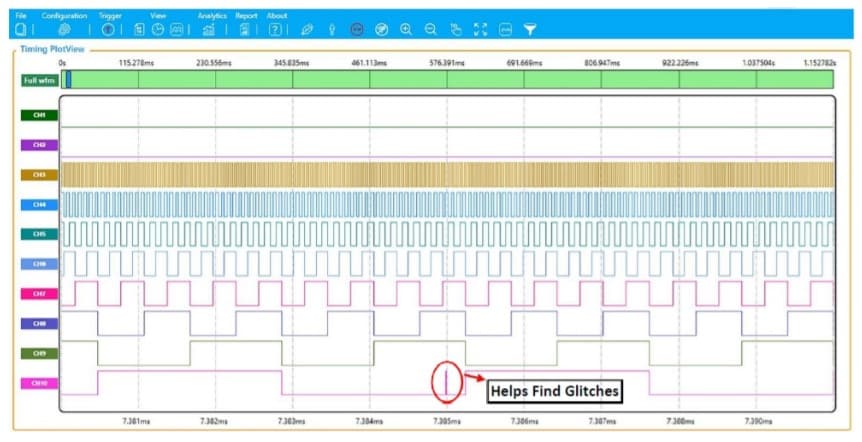

Timing-Ansicht

Die Timing-Ansicht ist eine einzigartige Funktion des PGY-LA-EMBD, die es Entwicklern ermöglicht, detaillierte Einblicke in die Timing-Informationen ihrer Signale zu erhalten. Die Timing-Ansicht verwendet ein internes Taktsignal zur Darstellung der Wellenform. Die flexible Auswahl der Abtastrate ermöglicht es Entwicklern, Glitches zu untersuchen, die Probleme bei der Funktion ihrer Designs verursachen können. Die Gruppierungsfunktion ermöglicht es Entwicklern, verschiedene verwandte Signale zur besseren Ansicht und Analyse zu gruppieren. Markierungs- und Zoomfunktionen erleichtern die Analyse von Timing-Fehlern. Die Möglichkeit, jeden beliebigen Punkt im erfassten Datensatz zu analysieren, gewährleistet eine einfache Fehlersuche und Analyse über eine lange Erfassungsdauer.

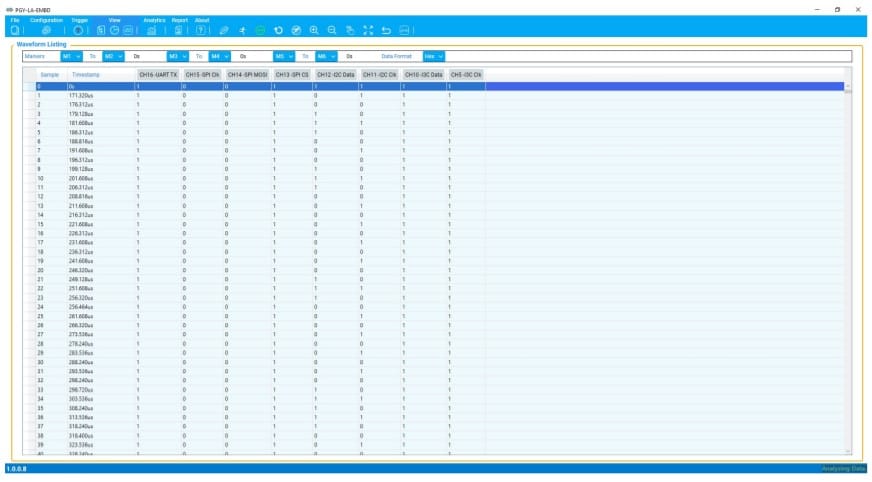

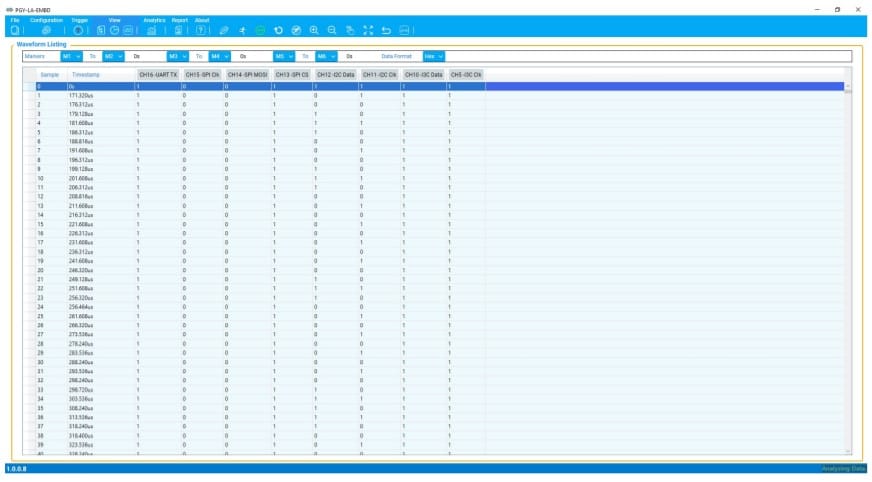

State View/Waveform Listing Ansicht

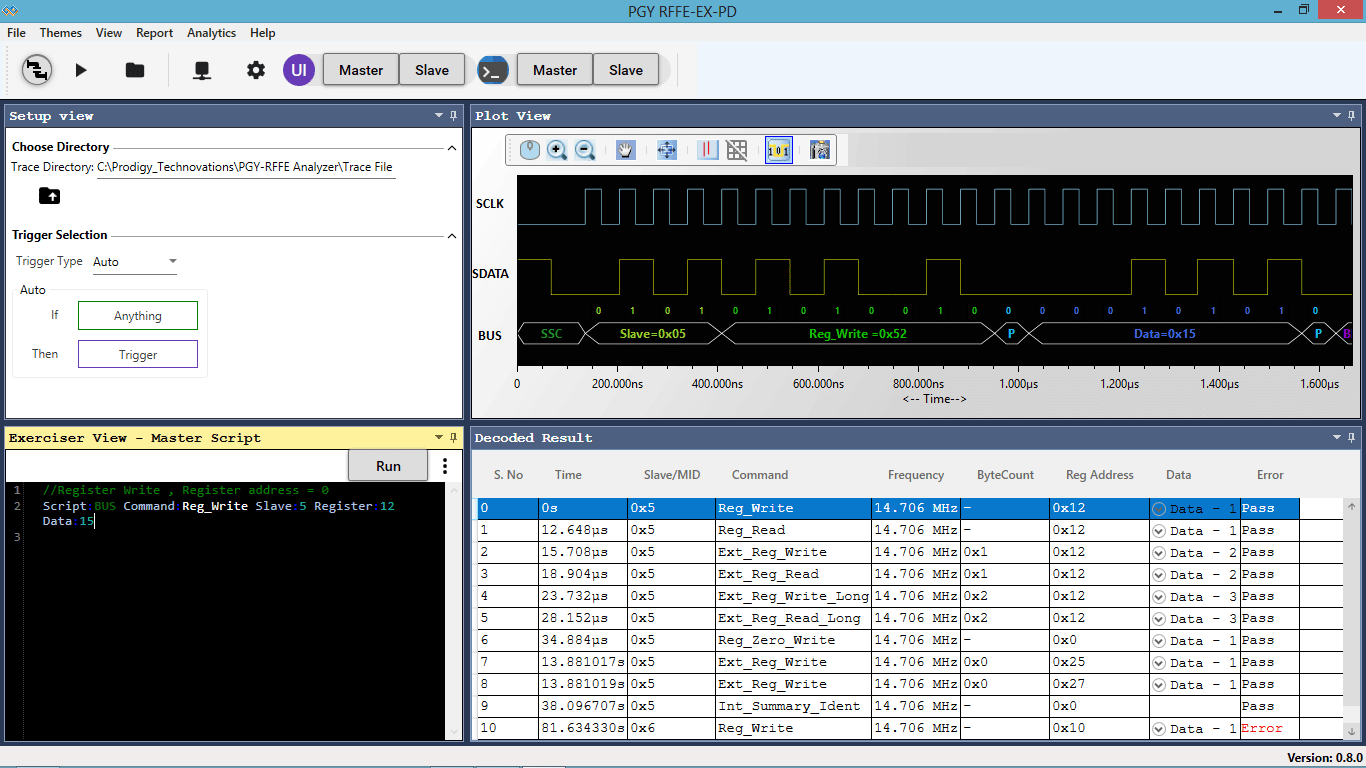

Protokoll-Dekodierungs Ansicht

Das Fenster "Protocol Activity" zeigt die dekodierten Paketinformationen in jedem Zustand und alle Paketdetails mit Fehlerinformationen in den Paketen. Dadurch erhalten die Entwicklungsteams einen Einblick auf Systemebene. Die einzelnen Fenster zur Protokolldekodierung basieren auf den ausgewählten Schnittstellen und gewährleisten eine einfache Anzeige für die Entwicklungsteams. Der ausgewählte Frame im Protokoll-Listing-Fenster wird in der Timing-Ansicht autokorreliert, um die Timing-Informationen des Pakets anzuzeigen. Protokollfehler werden hervorgehoben, um sicherzustellen, dass die Entwickler leicht auf sie aufmerksam gemacht werden.

Leistungsstarke Trigger-Funktionen

Report

Der Bericht kann im PDF- oder CSV-Format mit allen Signalinformationen, Plots und benutzerdefinierten Details wie Name des Unternehmens, Logo, Name des Testers, Datum und Uhrzeit erstellt werden, um sicherzustellen, dass die Designer alle Details dokumentieren und den Bericht weitergeben können.

Garantie

Für Hardware und Software gilt eine Garantie von einem Jahr. Sonden sind drei Monate Garantie für alle Herstellungsfehler abgedeckt

Technische Daten

| Spezifikation |  |

|---|---|

| Anzahl Kanäle | 16 Logikkanäle |

| Zustandsgeschwindigkeit | 1GS/s (asynchrone Erfassung) |

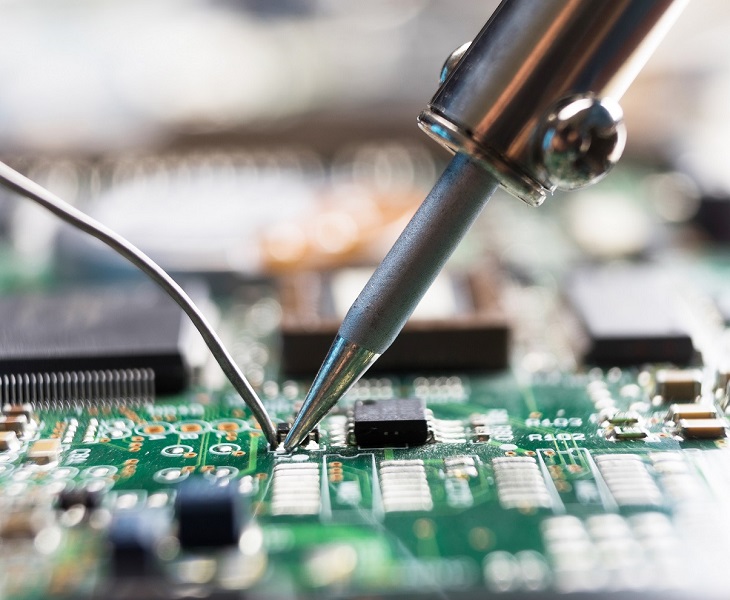

| Timing-Geschwindigkeit | Aktive Sonden einlöten |

| Anzahl der State-Clock-Unterstützung | Zweitens, Flexibilität zum Abtasten bei steigender oder fallender Flanke |

| Datensatzlänge | Smart Continuous Streaming von Daten auf HDD/SSD des Host-Computers |

| Spannungspegelunterstützung | 0 bis 5 V mit Flexibilität zur Definition des Logikschwellenwerts |

| Wellenformdiagramm | Zeigt Wellenformen mit flexibel konfigurierbarem Busdiagramm |

| Listenansicht | Listen Sie alle Datenstichproben an jedem Stichprobenpunkt auf |

| Trigger für LA | Mustertrigger, Impulsbreitentrigger, Verzögerungstrigger |

| Protokolldekodierungsunterstützung | I2C, SPI, UART, I3C, SPMI, CAN/CAN FD, RFFE |

| Gleichzeitige Dekodierung von I2C, SPI, UART | Ja, verbinden Sie den I2C-, SPI- und UART-Bus mit dem Logikanalysator. Erfasst gleichzeitig die Busdaten und zeigt sie an zeitkorrelierte Ansicht mit entsprechender Zeit Wellenformen. |

| Protokollansicht mit Timing-Ansicht (PA+LA) | Zeigt die protokolldekodierten Daten gleichzeitig mit hoher Abtastrate und Timing-Wellenform an |

| API-Unterstützung | Unterstützung für die Automatisierung des Betriebs mit Python und C++ |

| Verbindungstyp | Flying Lead Probe mit Buchsen #16 Micro Grabber Test Clips als optionales Zubehör |

| Externe Auslöser | Trigger-Out-SMA-Anschluss |

| Markierungen | Sechs, mit Delta-Informationen zwischen zwei Markierungen. |

| Aufrufe | Timing-Ansicht Zustands-/Logik-/Signallistenansicht Protokollansicht Bus-Diagramm zur Anzeige von Protokollpaketen mit Timing-Diagramm Plot Auto Trigger – Default (Trigger on any Paket) |

| Protokollauslöser | Musterauslöser Protokollbewusster Trigger- UART: Startbit, Paritätsbit, Daten SPI: MOSI-Daten, MISO-Daten I2C: START-Bit, Adresse, Daten, Adresse plus Daten, ACK, NACK, wiederholter START, STOP-Bit Timing-Parameter-Trigger: Impulsbreite (positiv oder negativ) Verzögerungstrigger. |

| Erfassungsdauer | Intelligentes Streaming von Protokolldaten zum Hosten von HDD/SSD. |

| Bericht | Berichterstellung im PDF- und CSV-Format |

| Host-Konnektivität | USB 3.0 Typ-C |

| Abmessungen | 115 mm x 90 mm x 25 mm |

| Gewicht | 300 g |