Management Data Input / Output (MDIO)

Management Data Input / Output (MDIO) ist ein serieller 2-Draht-Bus, mit dem PHYs oder Geräte der physischen Schicht in Media Access Controllern (MACs) in Gigabit-Ethernet-Geräten verwaltet werden. Die Verwaltung dieser PHYs basiert auf dem Zugriff und der Änderung ihrer verschiedenen Register.

MDIO wurde ursprünglich in Abschnitt 22 von IEEE RFC802.3 definiert. In der ursprünglichen Spezifikation kann eine einzelne MDIO-Schnittstelle auf bis zu 32 Register in 32 verschiedenen PHY-Geräten zugreifen. Diese Register bieten Status- und Steuerinformationen wie: Verbindungsstatus, Geschwindigkeitsfähigkeit und -auswahl, Ausschalten bei geringem Stromverbrauch, Duplexmodus (voll oder halb), automatische Aushandlung, Fehlersignalisierung und Loopback.

Um den wachsenden Anforderungen von 10-Gigabit-Ethernet-Geräten gerecht zu werden, wurden in Abschnitt 45 der 802.3ae-Spezifikation die folgenden Ergänzungen zu MDIO bereitgestellt:

- Zugriff auf 65.536 Register in 32 verschiedenen Geräten an 32 verschiedenen Ports

- Zusätzlicher OP-Code und ST-Code für den Zugriff auf das Register für indirekte Adressen für 10-Gigabit-Ethernet

- End-to-End-Fehlersignalisierung

- Mehrere Loopback-Punkte

- Elektrische Niederspannungsspezifikation

Theoretische Funktionweise

Der MDIO-Bus hat zwei Signale: Management Data Clock (MDC) und Managment Data Input / Ouput (MDIO).

MDIO verfügt über eine spezifische Terminologie zum Definieren der verschiedenen Geräte am Bus. Das Gerät, das den MDIO-Bus steuert, wird als Station Management Entity (STA) identifiziert. Die Zielgeräte, die vom MDC verwaltet werden, werden als MDIO Manageable Devices (MMD) bezeichnet.

Die STA initiiert die gesamte Kommunikation in MDIO und ist für das Ansteuern der Uhr auf MDC verantwortlich. MDC hat eine Frequenz von bis zu 2,5 MHz.

Klausel 22

Abschnitt 22 definiert das grundlegende Rahmenformat für die MDIO-Kommunikation (Abbildung Links), das sich aus den folgenden Elementen zusammensetzt.

| ST | 2 bits | Start of Frame (01 for Clause 22) |

| OP | 2 bits | OP Code |

| PHYADRESS | 5 bits | PHY Address |

| REGADRESS | 5 bits | Register Address |

| TA | 2 bits | Turnaround time to change bus ownership from STA to MMD if required |

| DATA | 16 bits | Data Driven by STA during write Driven by MMD during read |

Das Rahmenformat erlaubt nur eine 5-Bit-Nummer sowohl für die PHY-Adresse als auch für die Registeradresse, wodurch die Anzahl der MMDs begrenzt wird, an die die STA eine Schnittstelle herstellen kann. Darüber hinaus unterstützt Klausel 22 MDIO nur 5-V-tolerante Geräte und verfügt nicht über eine Niederspannungsoption.

Klausel 45

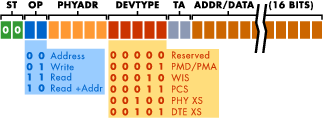

Um die Mängel von Abschnitt 22 zu beheben, wurde Abschnitt 45 zur 802.3-Spezifikation hinzugefügt. In Abschnitt 45 wurde die Unterstützung für Niederspannungsgeräte bis zu 1,2 V hinzugefügt und das Rahmenformat (Abbildung 14) erweitert, um den Zugriff auf viele weitere Geräte und Register zu ermöglichen. Einige der Elemente des erweiterten Rahmens ähneln dem Basisdatenrahmen:

| ST | 2 bits | Start of Frame (00 for Clause 45) |

| OP | 2 bits | OP Code |

| PHYADR | 5 bits | PHY Address |

| DEVTYPE | 5 bits | Device Type |

| TA | 2 bits | Turnaround time to change bus ownership from STA to MMD if required |

| ADDR/DATA | 16 bits | Address or Data Driven by STA for address Driven by STA during write Driven by MMD during read Driven by MMD during read-increment-address |

Die wichtigste Änderung in Abschnitt 45 ist der Zugriff auf die Register. In Abschnitt 22 gab ein einzelner Frame sowohl die Adresse als auch die zu lesenden oder zu schreibenden Daten an. Klausel 45 ändert dieses Paradigma. Zuerst wird ein Adressrahmen gesendet, um die MMD und das Register anzugeben. Ein zweiter Rahmen wird dann gesendet, um das Lesen oder Schreiben durchzuführen.

Das Hinzufügen dieses Zugriffs mit zwei Zyklen hat den Vorteil, dass Klausel 45 abwärtskompatibel mit Klausel 22 ist, sodass Geräte miteinander interagieren können. Zweitens wird durch Erstellen eines Adressrahmens der Registeradressraum von 5 Bit auf 16 Bit erhöht, wodurch eine STA auf 65.536 verschiedene Register zugreifen kann.

Um dies zu erreichen, wurden verschiedene Änderungen an der Zusammensetzung des Datenrahmens vorgenommen. Ein neuer ST-Code (00) wird definiert, um Datenrahmen von Klausel 45 zu identifizieren. Die OP-Codes wurden erweitert, um einen Adressrahmen, einen Schreibrahmen, einen Leserahmen oder einen Inkrement-Adressrahmen zum Lesen und Nachlesen anzugeben. Da die Registeradresse nicht mehr benötigt wird, wird dieses Feld durch DEVTYPE ersetzt, um den Zielgerätetyp anzugeben. Der erweiterte Gerätetyp ermöglicht der STA den Zugriff auf andere Geräte zusätzlich zu PHYs.

MDIO Protokoll Analyzer

Um ein System zu Debuggen ist ein Protokoll Analyzer oftmals die beste Lösung, um Fehler schnell zu entdecken und beheben zu können. Für das MDIO Protokoll bietet sich hierfür der Beagle I2C/SPI/MDIO Protokoll Analyzer von Total Phase an. Dieser ermöglicht dem Benutzer verzerrungsfreies Bus Monitorung. Nach dem der Beagle MDIO Protokoll Analyzer über USB mit dem PC verbunden wurde, lässt sich mit der zugehörigen Software (Data Center) der Busverkehr überwachen und analysieren. Dabei besitzt der MDIO Protokoll Analyzer einen internen Speicher indem er alle eingehenden Daten aufzeichnet und als einzigster auf dem Markt verfügbarer Protokoll Analyzer in Echtzeit anzeigen kann