- Demogerät verfügbar: Sie wollen das Gerät testen? Fragen Sie bei uns an, wir bieten Ihnen die Möglichkeit das Gerät bis zu 2 Wochen zu testen.

Beschreibung

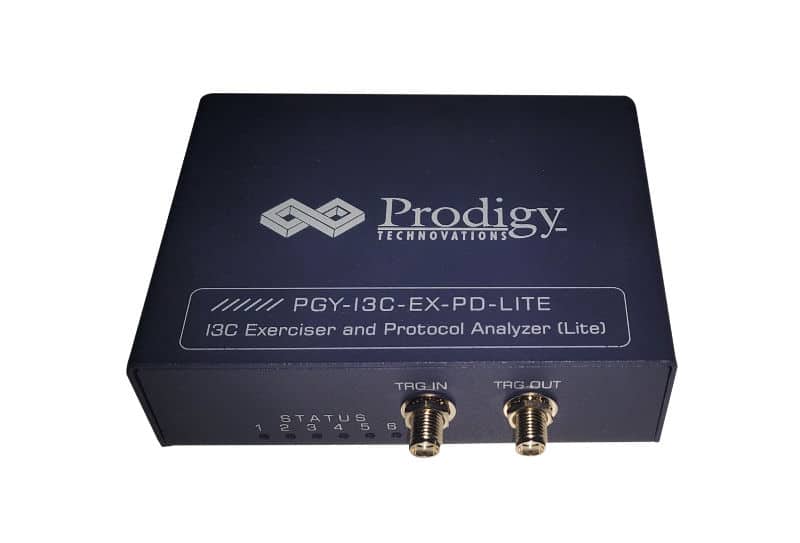

Der I3C Protocol Analyzer (PGY-I3C-EX-PD) verfügt über mehrere Funktionen zur Erfassung und Fehlersuche bei der Kommunikation zwischen dem Host und dem zu testenden Design. Die serielle I3C-Bus-Schnittstelle entwickelt sich zu einer bevorzugten Schnittstelle für alle zukünftigen Sensorverbindungen in der Mobiltelefon- und Automobilindustrie. Sie könnte auch als kostengünstige, zuverlässige Schnittstelle für künftige eingebettete elektronische Anwendungen eingesetzt werden, um die neuen datenintensiven Anwendungen zu bewältigen.

Die serielle I3C-Bus-Schnittstelle entwickelt sich zur bevorzugten Schnittstelle für alle künftigen Sensorverbindungen in der Mobiltelefon- und Automobilindustrie. Sie könnte auch als kostengünstige, zuverlässige Schnittstelle für zukünftige eingebettete elektronische Anwendungen gewählt werden, um die neuen datenintensiven Anwendungen zu bewältigen.

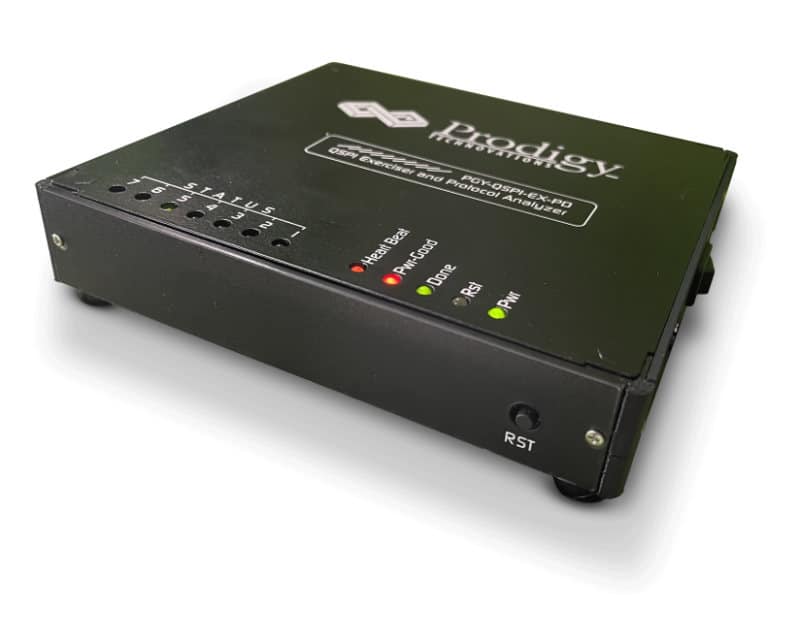

Das PGY-I3C-EX-PD ist das führende Instrument, mit dem Entwicklungs- und Testingenieure die I3C-Designs auf ihre Spezifikationen hin testen können, indem sie das PGY-I3C-EX-PD als Master/Slave konfigurieren, um I3C-Datenverkehr mit Fehlerinjektionsfunktionen zu erzeugen und I3C-Protokollpakete zu dekodieren.

Features I3C Protokoll Analyzer und Exerciser

- Unterstützt die I3C Spezifikation v1.0/v1.1

- Als Master oder Slave konfigurierbar.

- Möglichkeit zur Konfiguration der BCR-, LVR- und DCR-Register.

- Gleichzeitige Erzeugung des Datenverkehrs und Protokolldekodierung des I3C Busses.

- Optionale Unterstützung von Prüfskripten für die Einhaltung der MIPI Prüfvorschriften (CTS).

- Unterstützt I2C-Slaves und Master.

- Erzeugt verschiedene I3C SDR und HDR Pakete.

- Unterstützt IBI und Hot Plug Fähigkeiten.

- Fehlerinjektion wie CRC-Fehler, Paritätsfehler und ACK/NACK-Fehler.

- Variable I3C-Datengeschwindigkeiten und Duty Cycle.

- PMIC-Geräteunterstützung gemäß JEDEC DDR5-Spezifikation.

- Fähigkeit zum Margin-Test: Spannungs- und Zeitabweichung.

- Kontinuierliches Streaming von Protokolldaten zwischen dem Gerät und dem Host-Computer.

- Zeitdiagramm des protokolldekodierten Busses.

- Auflistung der Protokollaktivität.

- Fehleranalyse bei der Protokolldekodierung.

- Möglichkeit, ein Übungsskript zu schreiben, um die Erzeugung mehrerer Datenrahmen mit unterschiedlichen Datengeschwindigkeiten zu kombinieren.

- USB2/3-Schnittstelle für Host-Computer.

- API-Unterstützung für die Automatisierung in Python oder C++. 1 v1.1 unterstützt nur einspurige Befehle

v1.1 unterstützt nur one lane Befehle

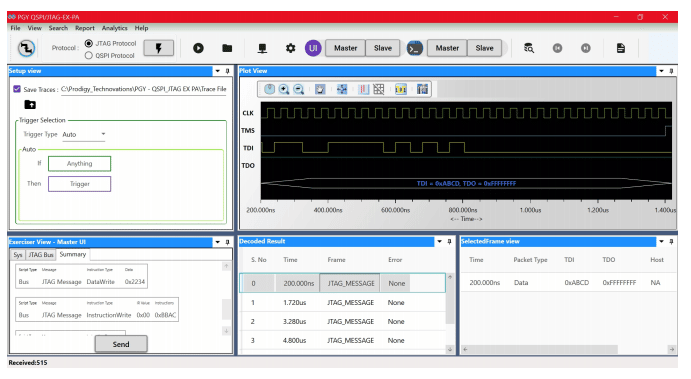

Multidomain-Ansicht

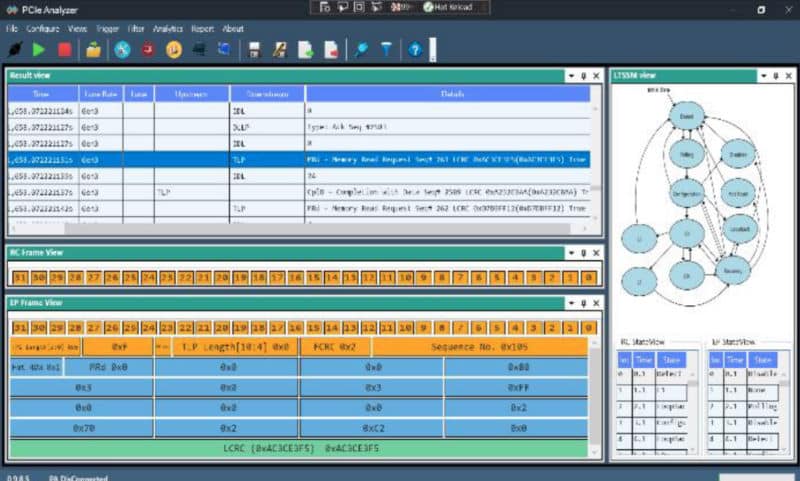

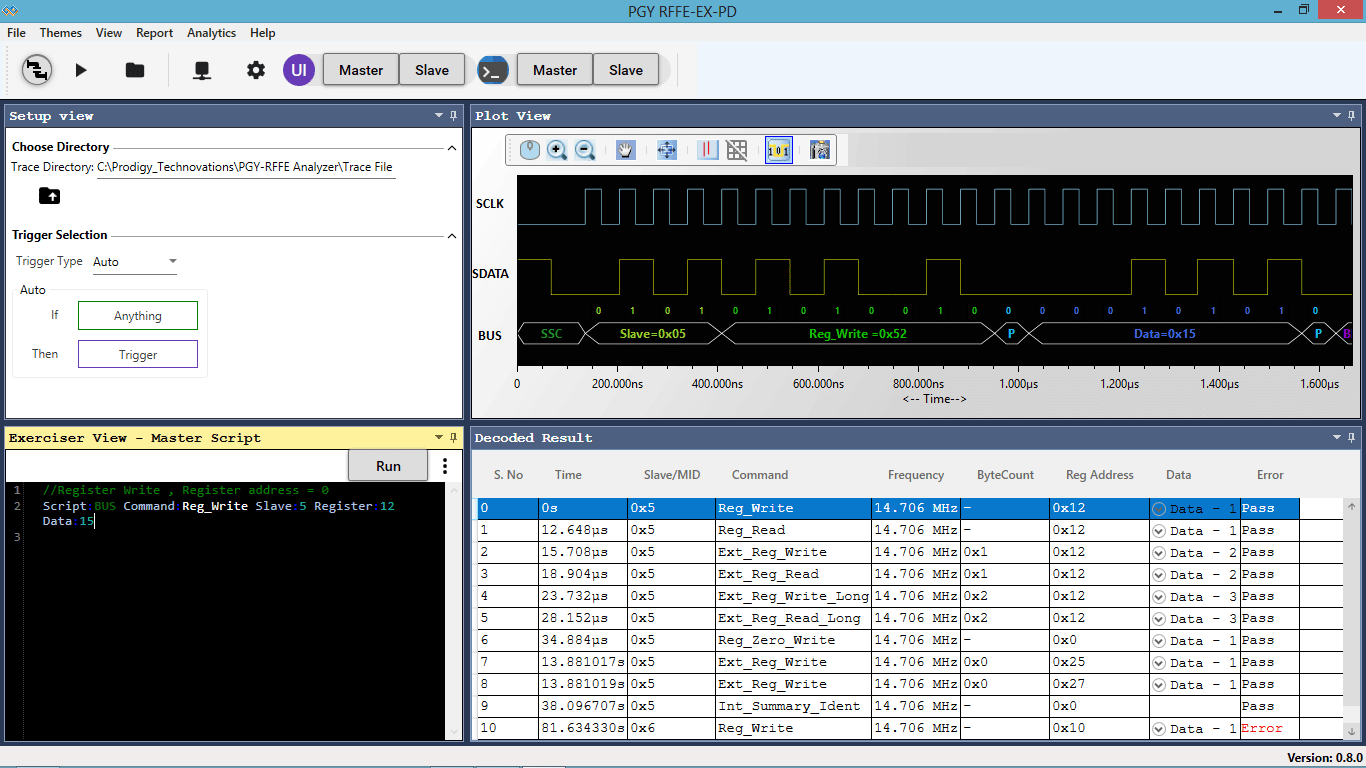

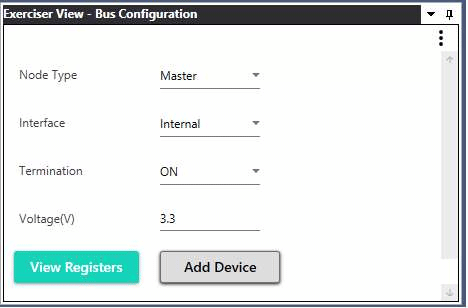

Die Multidomain-Ansicht bietet eine vollständige Übersicht über die I3C-Protokollaktivität in einer einzigen GUI. Benutzer können den Analyzer einfach einrichten, um I3C/I2C-Verkehr über die GUI oder ein Skript zu erzeugen. Der Benutzer kann im Setup-Menü verschiedene Trigger-Bedingungen einstellen, um die Protokollaktivität bei bestimmten Ereignissen zu erfassen und den Übergang zwischen Master und Slave zu dekodieren. Die dekodierten Ergebnisse können in den Fenstern Timing-Diagramm und Protokoll-Listing mit Autokorrelation angezeigt werden. Die State-Machine-Ansicht ermöglicht das Umschalten der State-Machine zwischen Master und Slave zur Design-Validierung. Diese umfassende Ansicht von Informationen macht es zu einem branchenweit besten Produkt und zu einer benutzerfreundlichen Lösung zum Debuggen der I3C-Protokollaktivität.

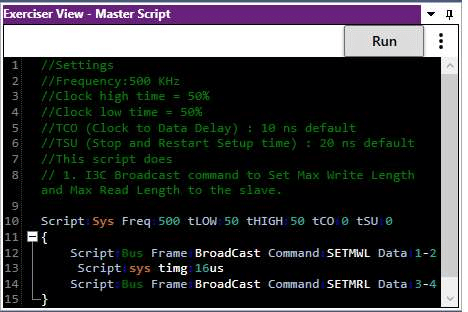

Exerciser

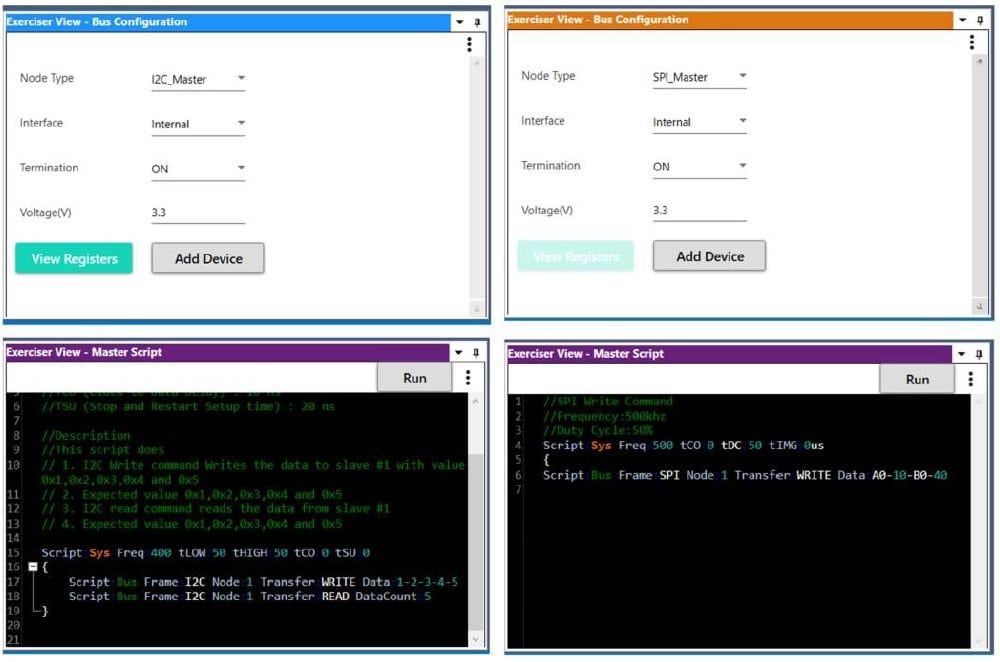

Das PGY-I3C-EX-PD unterstützt die Erzeugung von I3C-Datenverkehr mittels GUI und Skript. Benutzer können mit der GUI eine einfache Traffic-Generierung durchführen, um das DUT zu testen. Das skriptbasierte GUI bietet die Flexibilität, den gesamten erwarteten Datenverkehr in der realen Welt einschließlich Fehlerinjektionen zu emulieren. In dem folgenden Beispielskript kann der Benutzer I3C-Verkehr wie folgt erzeugen:

- Skriptzeile #10: Systemfrequenz 500KHz, Tastverhältnis auf 50%, CLK-zu-Daten-Verzögerung auf 10ns (Standard), Start-zu-Neustart-Setup-Zeit auf 20ns (Standard)

- Skriptzeile #12: SETMWL

- Skriptzeile #13: Systemintervall zwischen den Nachrichten auf 16us setzen

- Skript Zeile #14: SETMRL

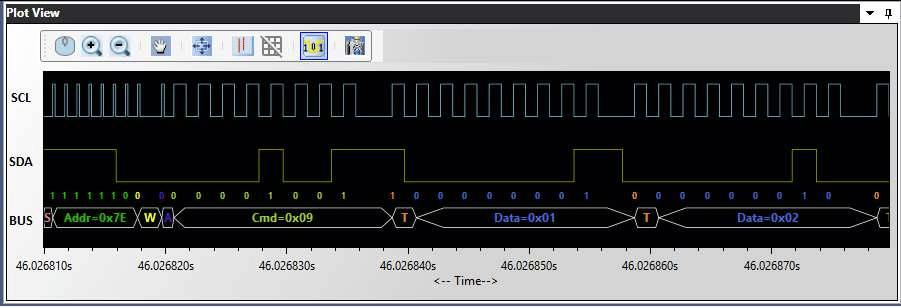

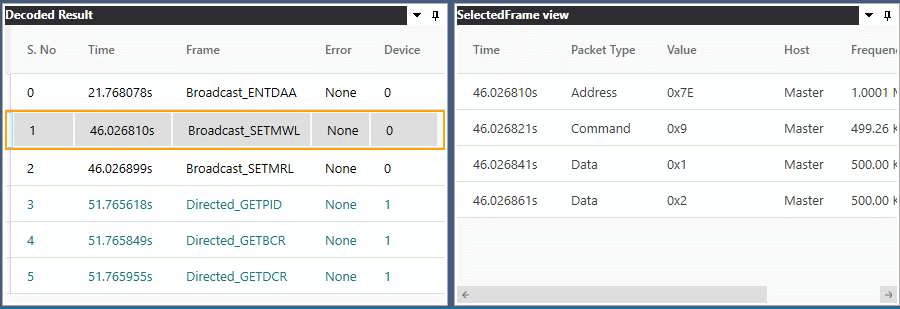

Timing Diagramm und Protokollauflistung

Die Timing-Ansicht bietet die Darstellung von SCL- und SDA-Signalen mit Busdiagramm-Informationen. Die Überlagerung von Protokollbits auf der digitalen Timing-Wellenform hilft bei der einfachen Fehlersuche in protokolldekodierten Daten. Cursor- und Zoom-Funktionen ermöglichen die bequeme Analyse des Protokolls in Timing-Diagrammen auf Timing-Fehler. Das Protokollfenster zeigt die dekodierten Paketinformationen in jedem Status und alle Paketdetails mit Fehlerinformationen im Paket an. Der ausgewählte Frame im Protokollfenster wird in der Timing-Ansicht automatisch korrigiert, um die Timing-Informationen des Pakets anzuzeigen.

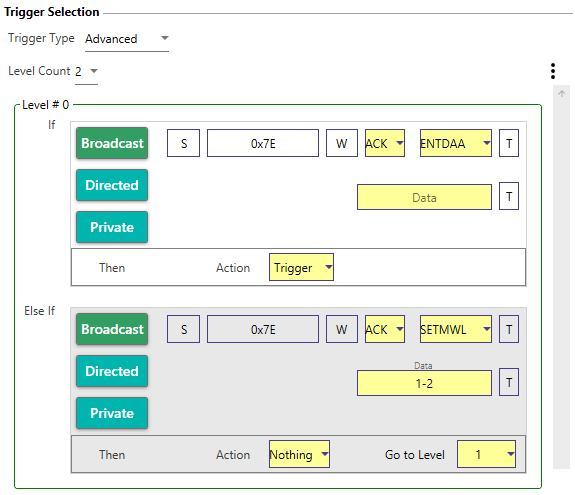

Leistungsstarke Trigger-Funktionen

PGY-I3C-EX-PD unterstützt automatische, einfache und erweiterte Triggerfunktionen. Das Analysegerät kann jedes der Protokollpakete auslösen, z. B. Broadcast, gerichtete oder private Nachrichten. Der erweiterte Trigger bietet die Flexibilität, mehrere Triggerbedingungen zu überwachen und kann Triggermaschinen mit mehreren Zuständen einstellen.

Mindestanforderungen Computer

Microsoft Windows® 8, Windows 7, 16GB RAM; Speicher mit mindestens 50 GB Festplattenspeicher für die Speicherung der erfassten Daten. Anzeige mit einer Auflösung von mindestens 1024x768.

Garantie

Für Hardware und Software gilt eine Garantie von einem Jahr. Sonden sind drei Monate Garantie für alle Herstellungsfehler abgedeckt

Technische Daten

| Spezifikation |  |

|---|---|

| Konfigurierbar | 1 Master + 3 Slave oder 1 sekundärer Master + 2 Slaves |

| I3C / I2C Traffic Generierung | Benutzerdefinierte I3C / I2C Traffic Generierung (Simulation des realen Netzwerkverkehrs) |

| SCL-Frequenz | 1Hz bis 12.5MHz - Das Prodigy-Gerät unterstützt bis zu 10MHz bei 1V Frequenz als Slave |

| Konfigurierbarer Spannungslevel | 0,9V bis 3,4V Schritte: A) 0.9 - 1.27 V (in Schritten von 5mV) B) 1,27 - 1,95 V (in Schritten von 10 mV) C) 1,95 - 3,4 V (in Schritten von 30 mV) |

| Hot Join | Ja |

| IBI | Ja |

| CCC-Unterstützung | Alle CCCs werden im Master Slide unterstützt. Alle CCC werden im Slave unterstützt, außer SETXTIME, ENTTM, ENTAS |

| Variation des SCL-Tastverhältnisses | Benutzerdefiniert (in Feinauflösung von 10ns) |

| SCL & SDA-Verzögerung | Benutzerdefiniert (in Feinauflösung von 18ps) |

| Verzögerung zwischen zwei Meldungen | Benutzerdefiniert (in feinen Auflösungen von ns, us, ms und Sekunden) |

| Fehlerinjektion | S0 bis S5 Fehlertypen, die in den I3C-Spezifikationen angegeben sind. CRC-Fehler im DDR-Verkehr. Präambel-Fehler im DDR-Verkehr ACK / NACK-Fehler (Slave) Master-Abbruch. Nicht-standardisierte Frames. Nicht standardmäßige Start-, Stop- und HDR-Ausgangsmuster, Slave-Reset Skripte speichern und laden. |

| API Support | Unterstützung für die Automatisierung des Betriebs mit Python oder C++ |

| Unterstützt | I3C & I2C Protokoll Dekodierung |

| Protokoll-Ansichten | Timing-Diagramm-Ansicht Protokoll-Listing-Ansicht Bus-Diagramm zur Anzeige von Protokollpaketen mit Timing-Diagramm-Darstellung |

| Dauer der Aufzeichnung | Kontinuierliches Streaming von Protokolldaten auf die Host-HDD/SSD |

| Protokoll-Fehlerbericht | S0 bis S5 Fehlertypen, die in den I3C-Spezifikationen angegeben sind CRC-Fehler im DDR-Verkehr Präambel-Fehler im DDR-Verkehr ACK /NACK-Fehler (Slave) Master-Abbruch Nicht-standardisierte Rahmen Nicht standardmäßige Start-, Stop- und HDR-Ausgangsmuster. |

| Host-Anbindung | USB 3.0 / 2.0 Schnittstelle |

.jpg)

.jpg)

.jpg)