Beschreibung

Der RFFE Protocol Analyzer (PGY-RFFE-EX-PD) ist ein Protokollanalysator mit mehreren Zusatzfunktionen zur Erfassung und Fehlersuche bei der Kommunikation zwischen Host und zu testendem Design. Die serielle Busschnittstelle RFFE (RF Front-End Control Interface) wird immer mehr zur Steuerung von RF-Front-End-Geräten eingesetzt. Es gibt eine Vielzahl von Front-End-Geräten wie Leistungsverstärker (PA), Low-Nose-Verstärker (LNA), Filter, Schalter, Power-Management-Module und Antennen-Tuner. Sie werden häufig in mobilen Geräten eingesetzt.

Features RFFE Protokoll Analyzer und Exerciser

- Unterstützt RFFE2.0/2.1 Spezifikation

- Kann als Master oder Slave konfiguriert werden

- Generierung verschiedener RFFE bei voller und halber Geschwindigkeit der vollen Frequenz

- Fehlerinjektion wie Paritätsfehler und ACK/NACK-Fehler

- Variable RFFE-Datengeschwindigkeiten

- Gleichzeitige Erzeugung von RFFE-Verkehr und Protokolldekodierung des Busses

- Das Zeitdiagramm des protokolldekodierten Busses

- Listing-Ansicht der Protokollaktivität

- Fehleranalyse bei der Protokolldekodierung

- Möglichkeit, ein Exerciser-Skript zu schreiben, um die Erzeugung mehrerer Datenrahmen mit unterschiedlichen Datengeschwindigkeiten zu kombinieren

- USB2/3-Host-Computer-Schnittstelle

- Flexibilität bei der Aufrüstung des Geräts für die Weiterentwicklung der RFFE-Spezifikation

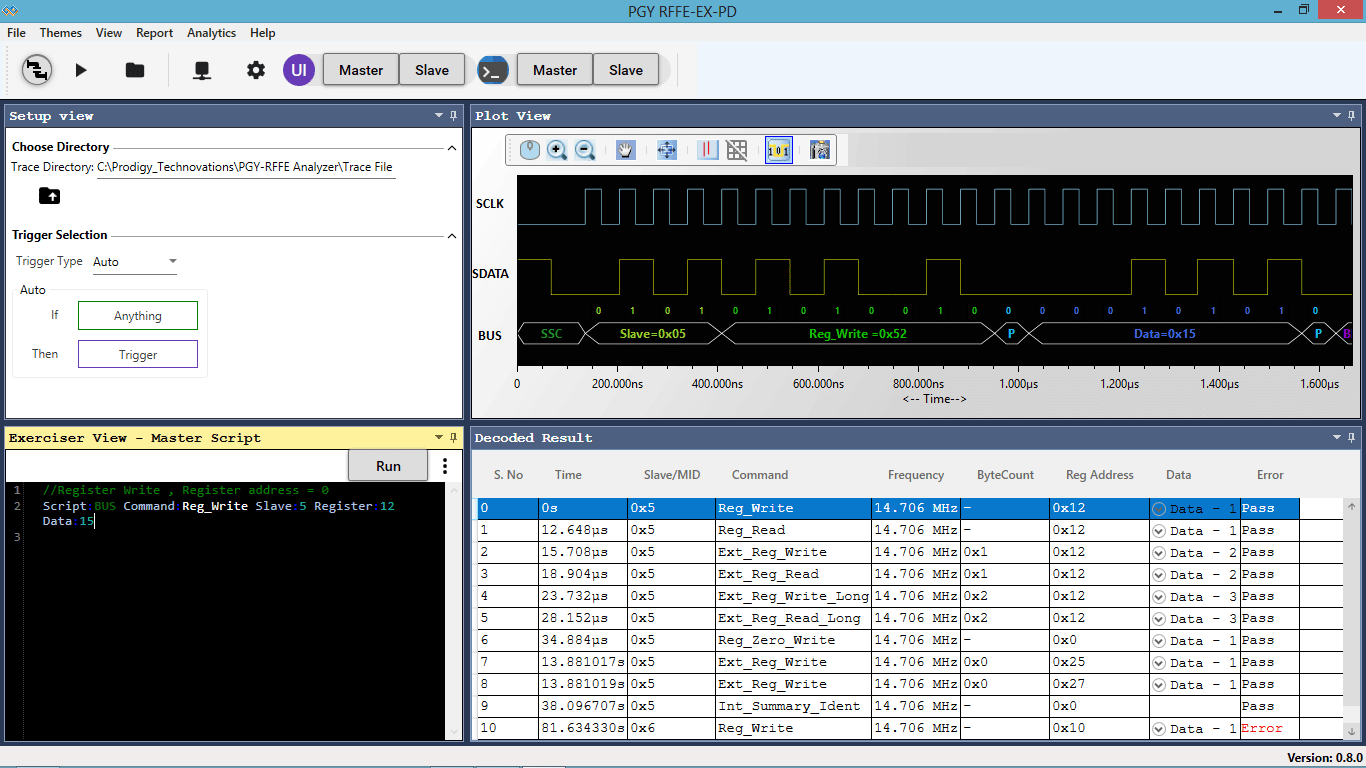

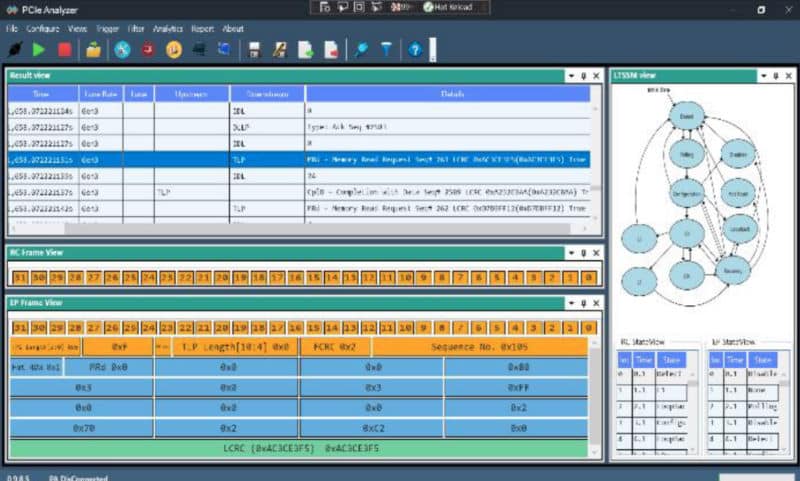

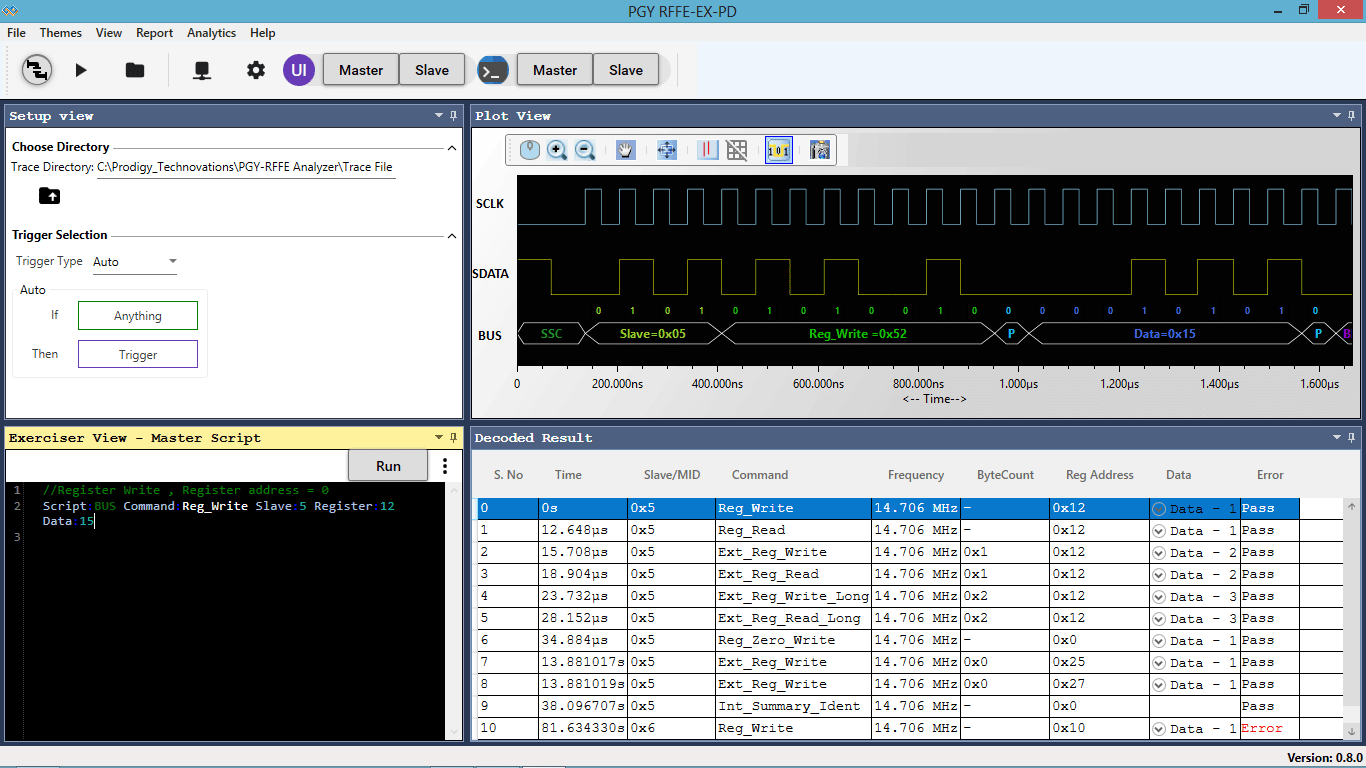

Multidomain-Ansicht

Die Multi-Domain-Ansicht bietet eine vollständige Ansicht der RFFE-Protokollaktivität in einer einzigen grafischen Benutzeroberfläche. Benutzer können den Analyzer leicht einrichten, um RFFE-Verkehr über eine GUI oder ein Skript zu erzeugen. Die Benutzer können im Setup-Menü verschiedene Trigger-Bedingungen einstellen, um die Protokollaktivität bei bestimmten Ereignissen zu erfassen und die Protokolltransaktionen zwischen Master und Slave zu dekodieren. Die dekodierten Ergebnisse können im Timing-Diagramm und im Protokoll-Listing-Fenster mit Autokorrelation angezeigt werden. Diese umfassende Informationsdarstellung macht die Software zu einer der besten in der Branche und bietet eine benutzerfreundliche Lösung zum Debuggen der RFFE-Protokollaktivität.

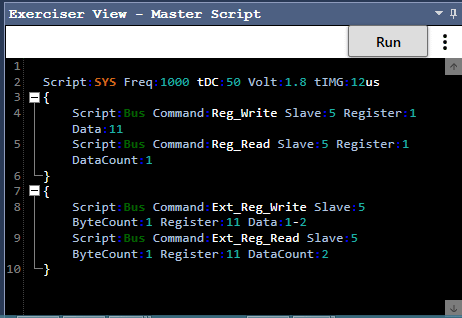

Exerciser

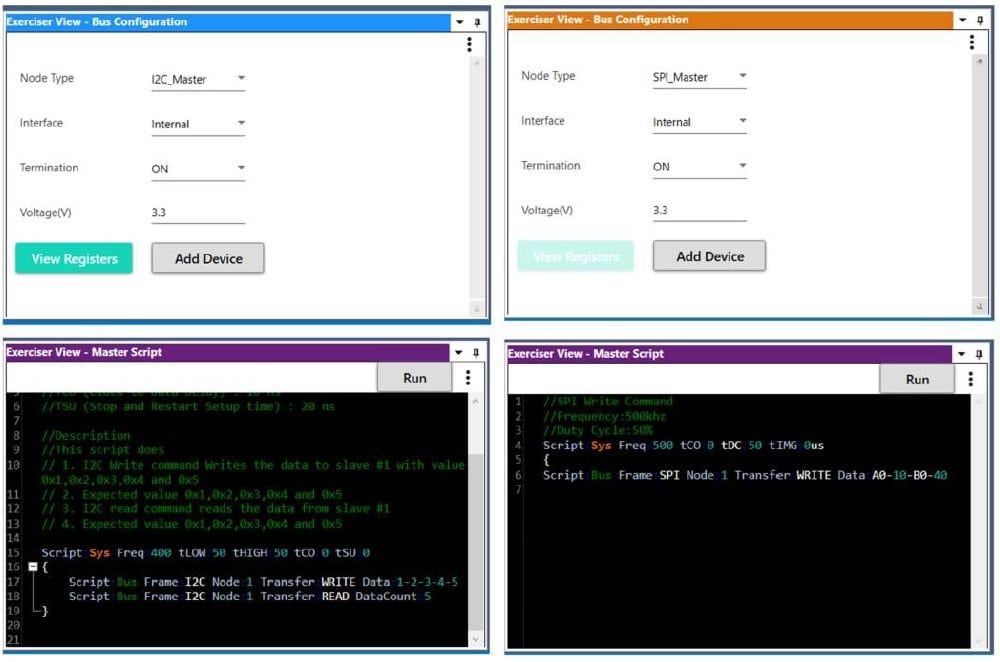

PGY-QSPI-EX-PD unterstützt die Erzeugung von QSPI-Verkehr mit Hilfe von GUI und Skript. Anwender können mit der GUI einfachen Datenverkehr erzeugen, um den Prüfling zu testen. Die skriptbasierte GUI bietet die Flexibilität, den gesamten erwarteten Datenverkehr in der realen Welt einschließlich Fehlerinjektionen zu emulieren. In diesem Beispielskript kann der Benutzer QSPI-Verkehr wie folgt erzeugen:

- Script line #4: REG Write to the slave with USID 5

- Script line #5: REG Read to the slave with USID 5

- Script line #8: EXT REG Write to the slave with USID 5

- Script line #9: EXT REG Read to the slave with USID 5

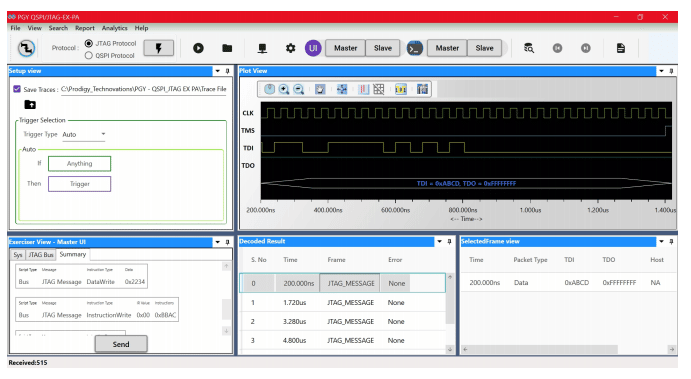

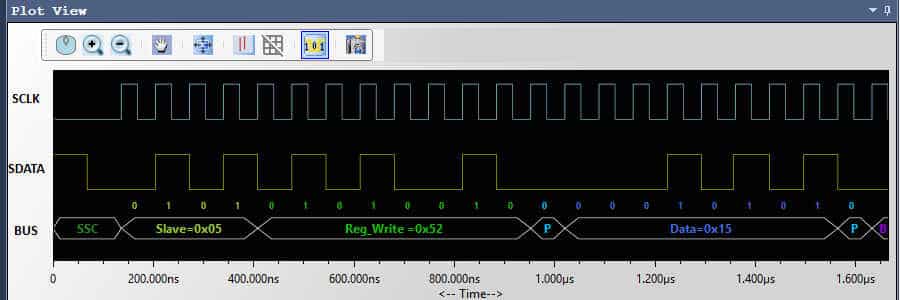

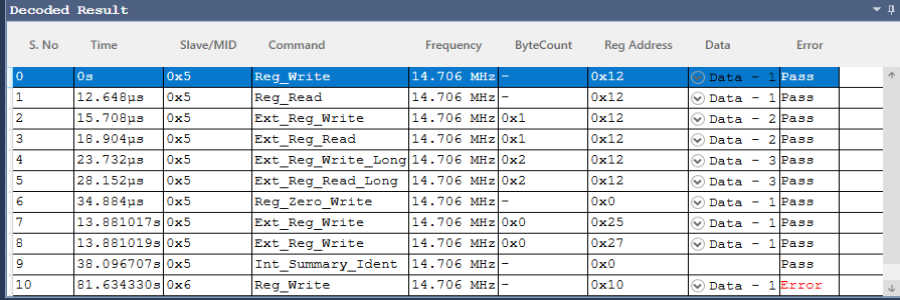

Timing Diagramm und Protokollauflistung

Die Timing-Ansicht bietet die Darstellung der SCLK- und SDATA-Signale mit einem Busdiagramm. Die Überlagerung der Protokollbits auf der digitalen Timing-Wellenform erleichtert die Fehlersuche bei den dekodierten Protokolldaten. Die Cursor- und Zoom-Funktionen erleichtern die Analyse des Protokolls im Timing-Diagramm auf eventuelle Timing-Fehler. Das Protokollfenster zeigt die dekodierten Paketinformationen in jedem Status und alle Paketdetails an. Der im Protokollfenster ausgewählte Rahmen wird in der Timing-Ansicht automatisch korrigiert, um die Timing-Informationen des Pakets anzuzeigen.

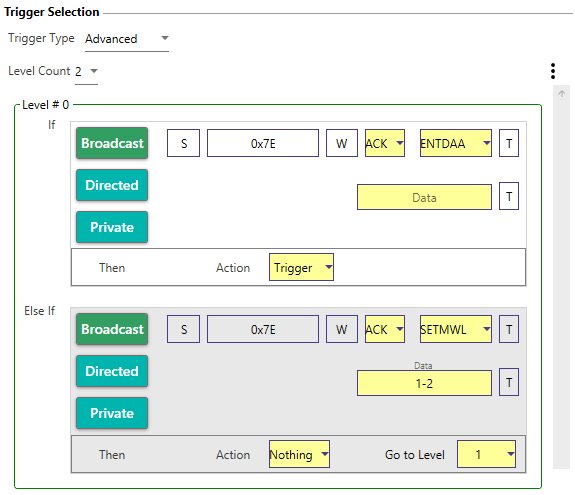

Leistungsstarke Trigger-Funktionen

PGY-RFFE-EX-PD unterstützt automatische, einfache und erweiterte Triggerfunktionen. Der Analysator kann auf jedes der Protokollpakete wie Ext. Reg. Write, Ext. Reg, Read und so weiter auslösen. Der erweiterte Trigger bietet die Flexibilität, mehrere Triggerbedingungen zu überwachen und kann Triggermaschinen mit mehreren Zuständen einstellen.

Garantie

Für Hardware und Software gilt eine Garantie von einem Jahr. Sonden sind Monate Garantie für alle Herstellungsfehler abgedeckt

Technische Daten

| Spezifikation | |

|---|---|

| Konfigurierbar | 1 Master + 4 Slaves |

| RFFE Traffic Generierung | Benutzerdefinierte RFFE-Traffic-Generierung |

| SCL-Frequenz | 32KHz bis 52 MHz |

| Konfigurierbarer Spannungslevel | 1,2 V und 1,8 V |

| SCL-Tastverhältnis-Variation | 25%, 50% and 75% |

| SCL & SDA Verzögerung | Benutzerdefiniert in Vielfachen von 5,2ns |

| Verzögerung zwischen zwei Meldungen | Benutzerdefiniert |

| Fehlerinjektion | Paritätsfehler-Injektion |

| Unterstützt | RFFE 2.0/2.1-Protokolldekodierung |

| Protokoll-Ansichten | Timing-Diagramm-Ansicht Protokoll-Listing-Ansicht Bus-Diagramm zur Anzeige von Protokollpaketen mit Timing-Diagramm-Darstellung |

| Protokoll Trigger | Auto (Auslösung bei jedem Paket) Einfach (Auslösung bei einem beliebigen benutzerdefinierten RFFE-Paket) Erweitert (Multi-state & mehrstufige Trigger Fähigkeit) |

| Erfassungsdauer | Kontinuierliches Streaming Protokoll |

| Protokoll-Fehlerbericht | Parität |

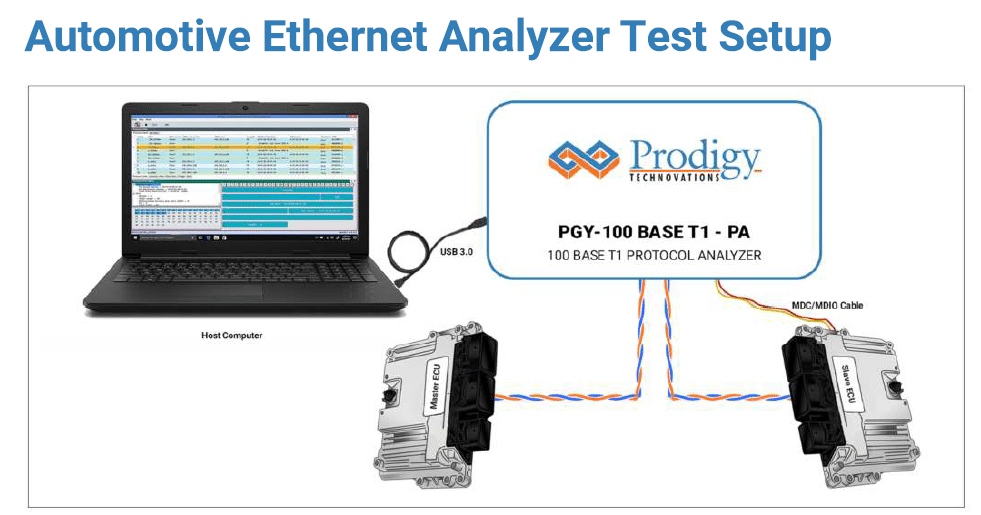

| Host-Verbindungen | USB 3.0 / 2.0 Schnittstelle |