Beschreibung

PMBus Protocol Analyzer (PGY-PMBus-EX-PD) ist ein Protokollanalysator mit mehreren Funktionen zur Erfassung und Fehlersuche bei der Kommunikation zwischen Host und zu testendem Design. Die PMBus-Schnittstelle ist eine ausgewählte Schnittstelle, die mit einer Vielzahl von Power-Management-Produkten wie AC-DC-Netzteilen und Lüftersteuerungen funktioniert.

PGY-PMBus-EX-PD ist das optimalste Messgerät, mit dem Design- und Testingenieure PMBus-Designs auf ihre Spezifikationen hin testen können, indem sie PGY-PMBus-EX-PD als Master/Slave konfigurieren, PMBus-Verkehr erzeugen und PMBus-Protokoll-Dekodierpakete dekodieren.

Features PGY-PMBus-EX-PD PM Protokoll Exerciser und Analyzer

- Unterstützt PMBus-Spezifikationen.

- Möglichkeit der Konfiguration als Master/Slave.

- Variable Datengeschwindigkeiten.

- Generierung von PMbus-Verkehr und Protokolldekodierung des Busses.

- Ein Zeitdiagramm des protokolldekodierten Busses.

- Auflistung der Protokollaktivität.

- Möglichkeit, ein Exerciser-Skript zu schreiben, um die Erzeugung mehrerer Frames mit unterschiedlichen Datengeschwindigkeiten zu kombinieren.

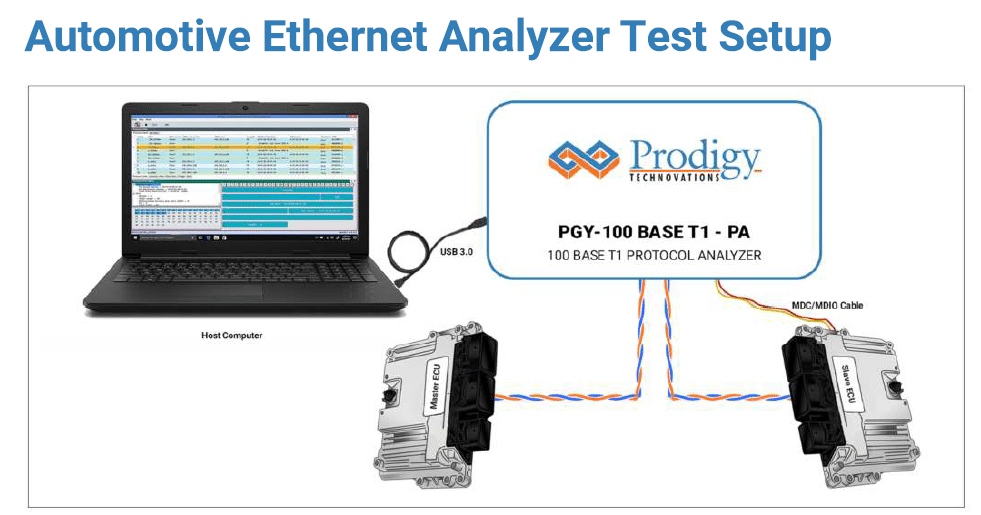

- USB 2/3 Schnittstelle zum Host-Computer.

- Kontinuierliches Streaming von Protokolldaten zum Host-Computer, um einen großen Puffer bereitzustellen.

- API-Unterstützung für die Automatisierung in Python oder C++.

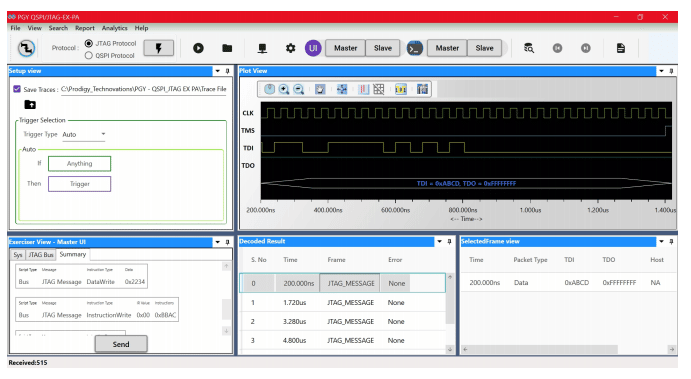

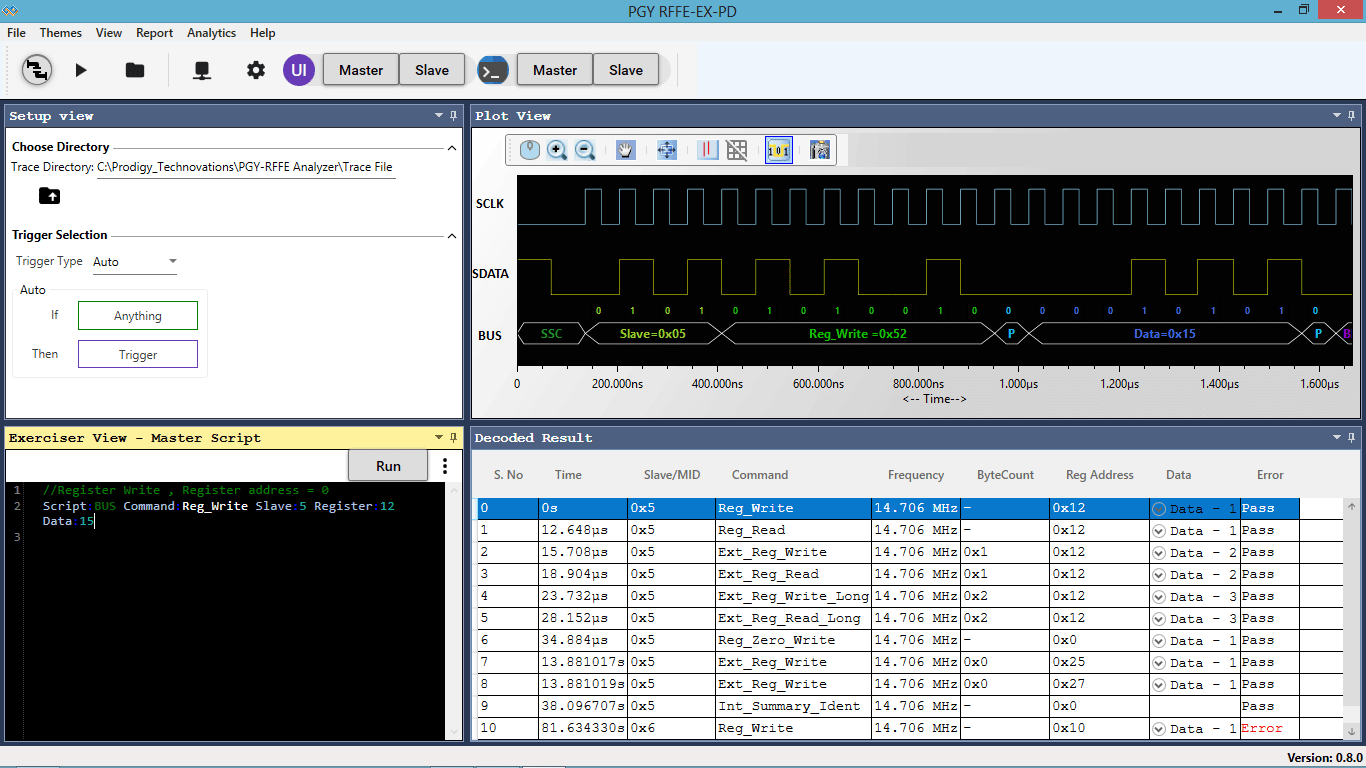

Umfassende Protokollanalyse mit Multi-View

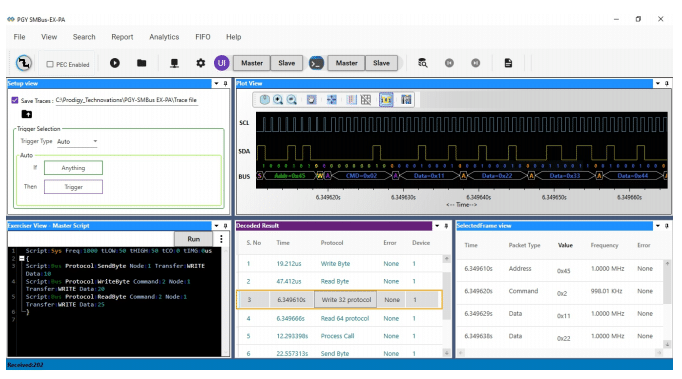

Die Multi-Domain-Ansicht bietet eine vollständige Ansicht der PMBus-Protokollaktivität in einer einzigen grafischen Benutzeroberfläche. Benutzer können den Analyzer einfach einrichten, um PMBus-Verkehr über eine GUI oder ein Skript zu erzeugen. Der Benutzer kann im Setup-Menü verschiedene Trigger-Bedingungen einstellen, um die Protokollaktivität bei bestimmten Ereignissen zu erfassen und den Übergang zwischen Master und Slave zu dekodieren. Die dekodierten Ergebnisse können im Timing-Diagramm und im Protokoll-Listing-Fenster mit Autokorrelation angezeigt werden. Diese umfassende Ansicht der Informationen macht es zu einem der besten in der Branche und bietet eine benutzerfreundliche Lösung zum Debuggen der PMBus-Protokollaktivität.

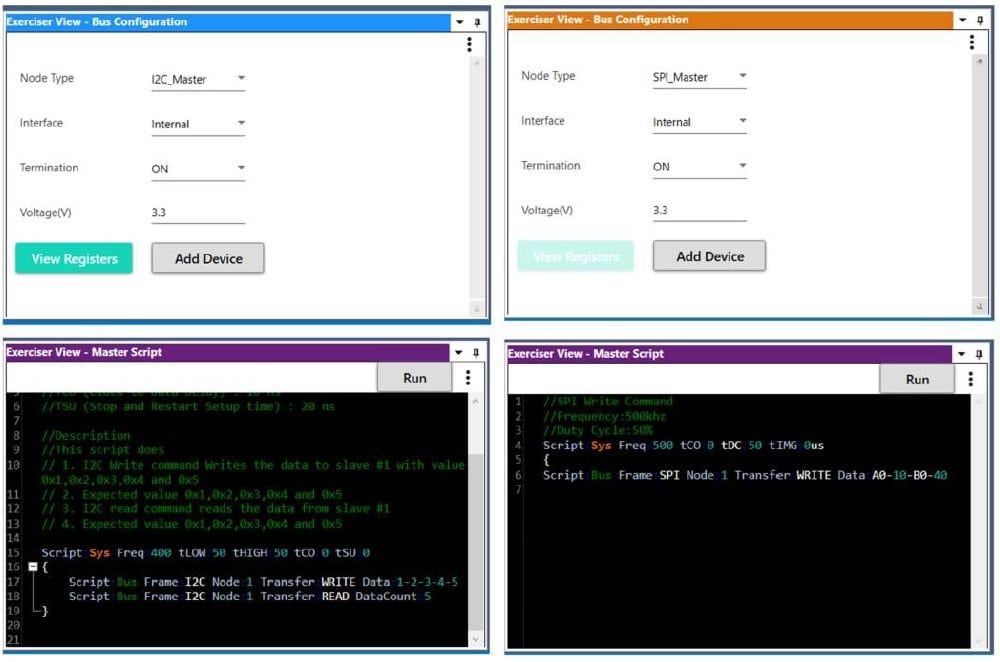

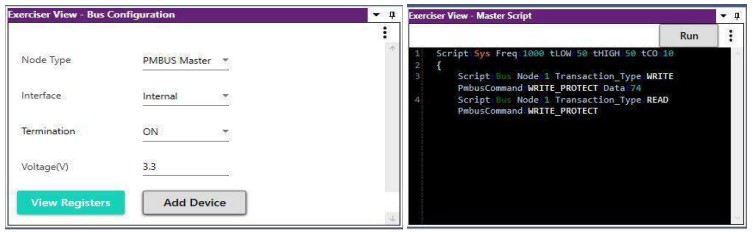

Exerciser

PGY-PMBus-EX-PD supports PMBus traffic generation using GUI and Script. Users can generate simple traffic generation using the GUI to test the DUT. Script-based GUI provides flexibility to emulate the complete expected traffic in the real world including error injections. In this sample script user can generate PMBus traffic as below:

- Script line #1: Set system Frequency 1MHz, Duty cycle to 50%, CLK to data delay to 10ns

- Script line #3: WRITE Transaction_Type

- Script line #4: READ Transaction_Type

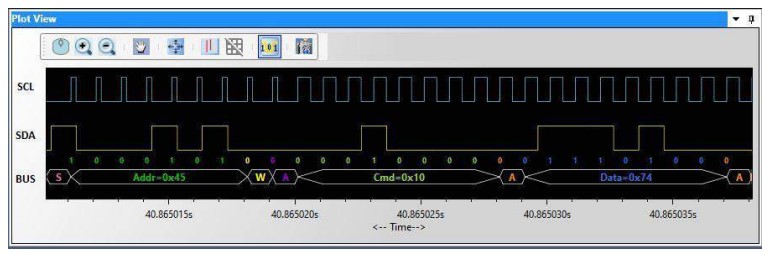

Ansicht des Zeitdiagramms und der Protokollauflistung

Die Timing-Ansicht bietet die Darstellung der SCL- und SDA-Signale mit einem Busdiagramm. Die Überlagerung der Protokollbits auf der digitalen Timing-Wellenform erleichtert die Fehlersuche bei den dekodierten Protokolldaten. Die Cursor- und Zoom-Funktionen erleichtern die Analyse des Protokolls im Timing-Diagramm auf eventuelle Timing-Fehler.

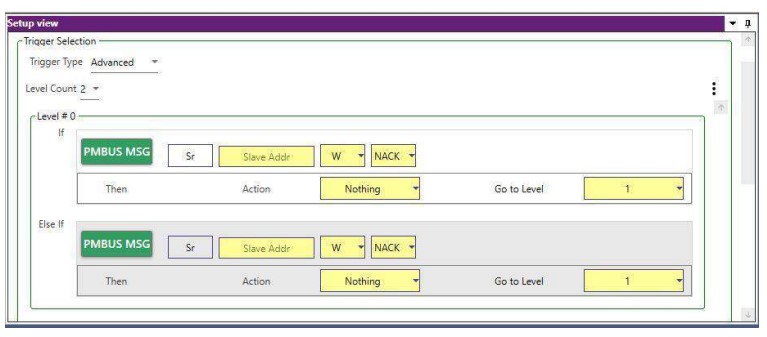

Leistungsstarke Triggerfunktionen

PGY-PMBus-EX-PD unterstützt automatische, einfache und erweiterte Triggerfunktionen. Der Analysator kann auf jedes der PMBus-Protokollpakete triggern. Der erweiterte Trigger bietet die Flexibilität, mehrere Triggerbedingungen zu überwachen und kann Triggermaschinen mit mehreren Zuständen einstellen.

Garantie

Für Hardware und Software gilt eine Garantie von einem Jahr. Sonden sind drei Monate Garantie für alle Herstellungsfehler abgedeckt