Beschreibung

Merkmale PCIe Low Power Side Band Signal Analyser

- Kostengünstiger Logikanalysator mit kontinuierlicher Streaming-Funktion zur Überwachung von Seitenbandsignalen

- Zeichnet die Timing-Wellenformen von PWR, CLKREQ, PERSET und REFCLK auf

- Power-ON Zustand

- Neustart

- Stromsparender Ein- und Austritt aus dem und in den L0-Zustand

- Misst Timing-Parameter

- Signalisiert den Ausfall von Timing-Parametern

- Auslöser für den Ausfall von Timing-Parametern

- Unterstützung für Berichte mit geringer Latenz zum Überschreiben von T-CRON-Parametern

- Berichtserstellung

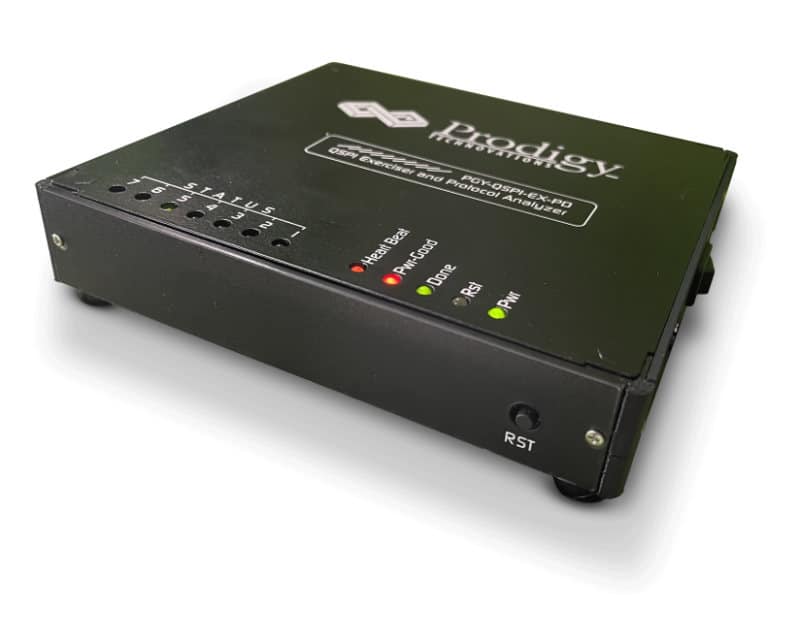

PGY-PCIeLP-SBA verfügt über eine M.2-Extenderkarte mit Zugriff auf alle Seitenbandsignale, die an den PCIe Low Power Sideband Signal Analyser angeschlossen werden können. Die Software läuft auf einem Windows-PC und ermöglicht es, den Analysator für Messungen und Triggerbedingungen zu konfigurieren. Sie zeichnet kontinuierlich die Timing-Wellenformen auf und aktualisiert die Timing-Messübersicht mit statistischen und detaillierten Informationen.

Konfigurationspanel

Die Konfiguration ermöglicht es den Nutzern, die zu messenden Timing-Parameter einfach auszuwählen und den Trigger festzulegen, wenn diese Parameter ausfallen. Der Nutzer kann die Dauer der Aufzeichnung festlegen (sie kann mehrere Stunden betragen) oder die Analyse manuell stoppen. Die Auswahl von Pre- und Post-Trigger bietet die Möglichkeit, die Daten rund um die Triggerbedingung zu betrachten.

PGY-PCIeLP-SBA bietet leistungsstarke Debugging-Funktionen, mit denen der Benutzer Fehler in den aufgezeichneten Daten erkennen kann:

- Verknüpfung der spezifischen Messung mit der Timing-Wellenform mithilfe von Markern

- Sortieren der spezifischen Messung, um alle Treffer anzuzeigen

- Sortieren von fehlgeschlagenen oder erfolgreichen Messungen

- Unterstützung des Latenztoleranzberichts

Garantie

Für Hardware und Software gilt eine einjährige Garantie. Für die Sonden gilt eine monatliche Garantie auf alle Herstellungsfehler

Technische Daten

| Spezifikation |  |

|---|---|

Messparameter | Parameter Beschreibung |

TCRH AUS | CLQREQ# de-asserted high to clock geparkt |

TCRL EIN | CLQREQ# wird auf Low gesetzt, um die Uhr zu aktivieren |

TPVGL | Power Valid bis PERST# Eingang aktiv |

TPERST#CLK | REFCLK stabil vor PERST# Deassertion |

TPERST | Durchsetzungszeit von PERST# |

.jpg)

.jpg)

.jpg)