Beschreibung

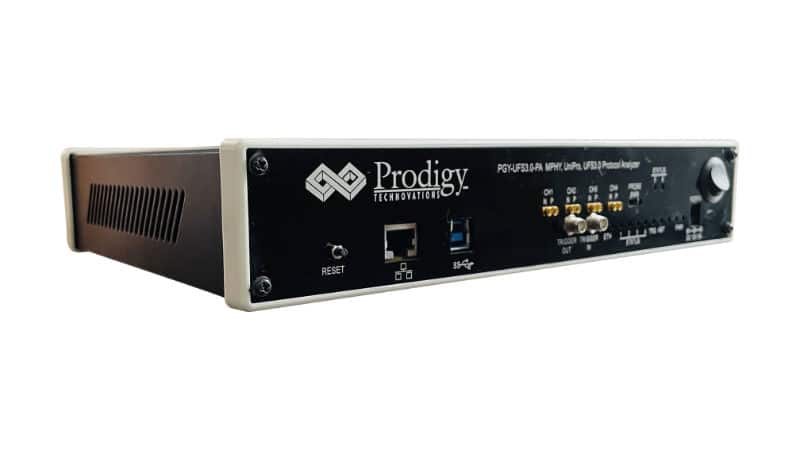

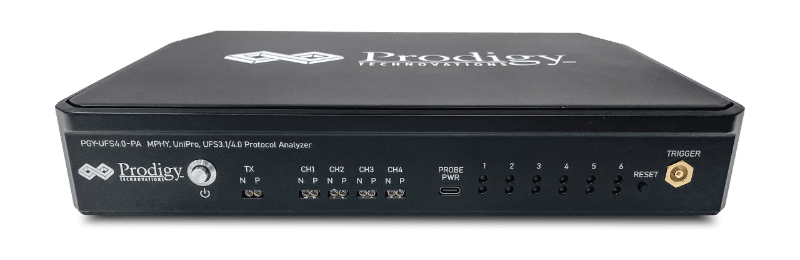

Der Protokollanalysator mit mehreren Funktionen zur Erfassung und Fehlersuche bei der Kommunikation zwischen Host und den zu testendem SDIO (Secure Digital Input Output) und eMMC Speicher. Der SDIO Protocol Analyzer unterstützt Datenraten bis zu 200MHz (HS400) DDR-Modus.

Der innovative aktive Tastkopf belastet das zu prüfende Bauteil (DUT) nur minimal elektrisch und ermöglicht die Protokolldatenerfassung, ohne die Leistung des Testobjekts zu beeinträchtigen. Mit einer branchenweit einmaligen Funktion ermöglicht der PGY-SSMlite-SDIO Protokoll Analyzer das kontinuierliche Streaming der Protokolldaten, über die USB3.0- oder GbE-Schnittstelle, auf den Computer mit der Protokollsoftware. Die umfangreiche Dekodierung von Protokolldaten, Kommandodaten und der Real-Time Fehleranalyse ermöglicht eine effektive Verifizierung der Kommunikation zwischen den SDIO-Host und dem Speichermedium.

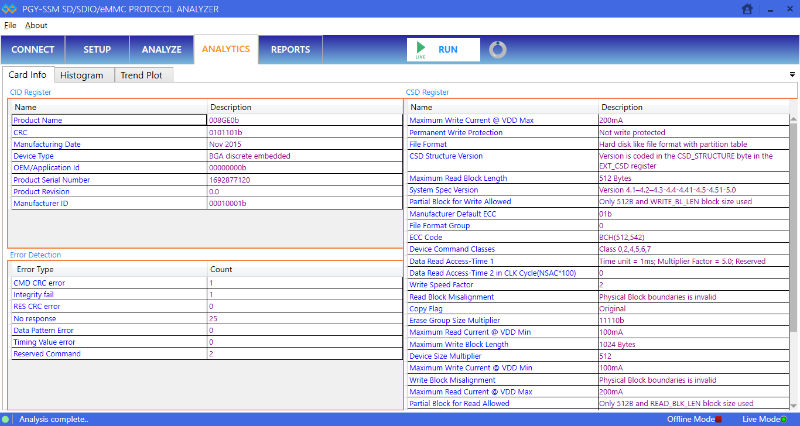

Der Protokoll Analyzer ermöglicht es Entwicklungs- und Verifikationsingenieuren, SDIO zu testen und zu debuggen, indem sie auf Command, Response, Daten oder auf CRC-Fehler triggern. Er ermöglicht auch die sofortige Dekodierung von Command, Response, CID-, CSD- und Ext-CSD-Registern. Die Analysefunktion bietet dabei eine einfach zu analysierende grafische Anzeige der Command, Response, Daten und Betriebsfrequenz für die erfasste Dauer.

Unterstützte Protokolle:

- SDIO 4.0

Features SDIO Protokoll Analyzer

- Kontinuierliche Überwachung der Protokolldaten über einen langen Zeitraum zur Aufzeichnung schwer zu erfassenden Ereignissen (mehr als 30 GB Datenerfassung)

- Analyse der aufgenommenen Daten auf Basis von Standards wie Protokollintegrität, Anzahl der Datenbursts, CMD und CRC-Fehler, Response CRC-Fehler, Daten CRC-Fehler, Timing-Werte und reservierten Kommandos.

- Die hardwarebasierte, protokollgesteuerte Triggerfunktion in Echtzeit ermöglicht die Erfassung bestimmter Events z.B. das Auslösen von Patterns, Kommandos oder Fehlermeldungen.

- Der Benutzer kann Anomalien durch die Dekodierung der Command- und Response-Argumente herausfinden.

- Die Analysefunktion ermöglicht die Auswertung der erfassten Protokolldaten durch die Darstellung von Command, Response, Daten, und Betriebsfrequenz über die Zeitachse.

- Die Analysefunktion bietet auch die Dekodierung der Bauteileregister an.

- Filter ermöglichen das bestimmte Pakete in den dekodierten Protokollpaketen angezeigt werden.

- Suchfunktion für spezifische Ereignisse auf der Protokollebene

- Die einfach zu bedienende Benutzeroberfläche spart Zeit bei der Einarbeitung.

- Ermöglicht eine Langzeiterfassung und zeigt die dekodierten Daten an, ohne umfangreiche Ressourcen im Host-Computer in Anspruch zu nehmen.

- Das Einfügen von Markern[mit Trigger-In] hilft bei der Zuordnung des digitalen Eingangssignals mit der Protokollaktivität.

- Das Trigger-Out Signal für jedes spezifische Protokollereignis ermöglicht die Ansteuerung anderer Instrumente, wie z.B. ein Oszilloskop.

- Schnittstelle zum Computer mit der ausgeführten Software über eine USB3.0 oder Gigabit-Ethernet-Schnittstelle

- Die GbE-Schnittstelle bietet eine einfache und flexible Upgradefunktion der Firmware.

- Export von dekodierten Datenpaketen in eine.txt-Datei zur weiteren Analyse

Der Aufbau

Der Protokoll Analyzer PGY-SSMlite-SDIO arbeitet nach dem Prinzip der Fat-Pipe Analyse, bei der die Analyzator-Probes auf den Interface-Bus zwischen Host und dem zu prüfenden Gerät [Speicher] angeschlossen werden. Er erfasst alle Transaktionen, die zwischen dem Host und Speicher stattfinden, und führt eine Echtzeitanalyse auf Fehler durch und eine detaillierte Analyse der erfassten Daten. Diese werden über die Softwareoberfläche im angeschlossenen Computer dargestellt. Die erfassten Daten werden auf der Festplatte des Computers gespeichert und damit eine lange Aufzeichnung ermöglicht. Bitte reservieren Sie genügend freien Speicher auf der Festplatte. Der PGY-SSMlite-SDIO Protokoll Analyzer kann mit dem Computer über USB3.0[Super Speed] und GbE verbunden werden.

Probing

Der PGY-SSMlite-SDIO Protokollanalysator verfügt über einen aktiven Tastkopf der eine sehr schnelle und flexible Messdurchführung, bei minimaler elektrischer Belastung des Messobjekts, ermöglicht. Dieser wurde speziell auf die Anforderung bei der Überprüfung von SDIO-Signalen abgestimmt. Die Probes unterstützen 200MHz DDR-Bandbreite damit SDIO-Signale fehlerfrei erfasst werden können. Die Probes haben ein bewegliches Sondenkabel mit Bergpoststecker und lötbaren Sondenspitzen. Dies macht den Anschluss an das Messobjekt sehr einfach

Umfangreiche Protokollanalyse

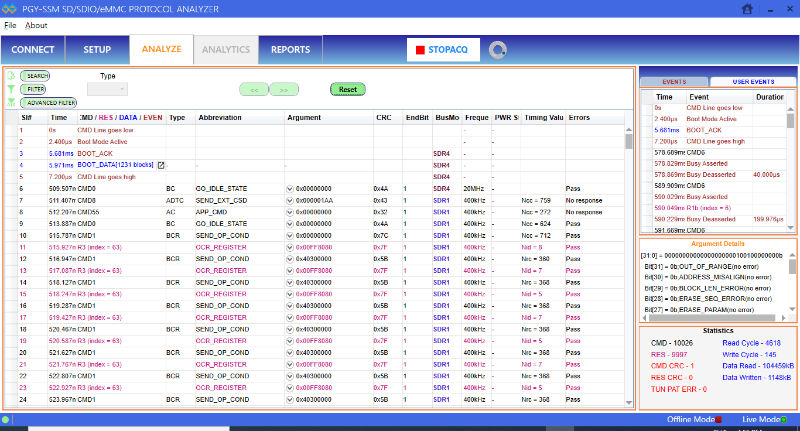

Die PGY-SSMlite-SDIO Software bietet die branchenweit besten Protokollanalyse-Funktionen. Eine einfach zu bedienende Schnittstelle reduziert die Komplexität und Zeit für das Protokoll-Debugging. Die zeitgesteuerte Anzeige der Dekodier-Auflistung bietet eine vollständige Ansicht der Protokollaktivitäten zwischen Host und Gerät. Durch Anklicken der Auswahlaufforderungen kann der Anwender die Dekodierung von Argumenten, CSD, CID-Registern, Datenaktivitäten und mehr erhalten.

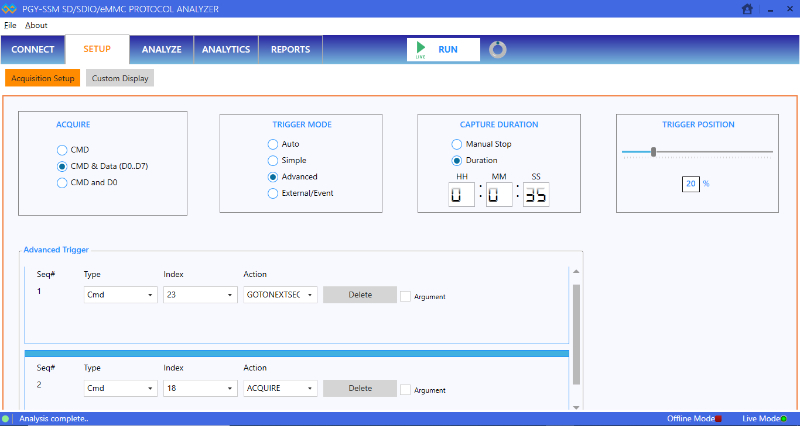

Protokolldatenerfassung und Triggerung

Der PGY-SSMlite-SDIO Protocol Analyzer verfügt über leistungsstarke protokollgesteuerte Triggerfunktionen, die es erlauben, Protokollereignisse bei bestimmten Events zu erfassen. Der PGY-SSMlite-SDIO unterstützt einfache und erweiterte Trigger-Funktionen. Der PGY-SSMlite-SDIO kann einen bestimmten Befehl, eine bestimmte Antwort oder eine CRC-Fehlerbedingung auslösen. Die erweiterten Triggerfunktionen ermöglichen es, dass die sequentielle Triggerbedingung Protokolldaten nach einer Reihe von Events erfasst. Im Automatikmodus werden die Daten beim Drücken der Run-Taste erfasst.Die Dauer der Protokolldatenerfassung wird durch einen manuellen Stopp oder das Einstellen der Aufzeichnungsdauer gesteuert. Beim Einstellen der Aufzeichnungsdauer stellt der Benutzer die Datenerfassung zwischen 3 Sekunden und 4 Stunden ein. Während des Aufnahmemodus werden die Protokolldaten kontinuierlich auf die Festplatte des Hostsystems übertragen und gespeichert.

Analysefunktionen

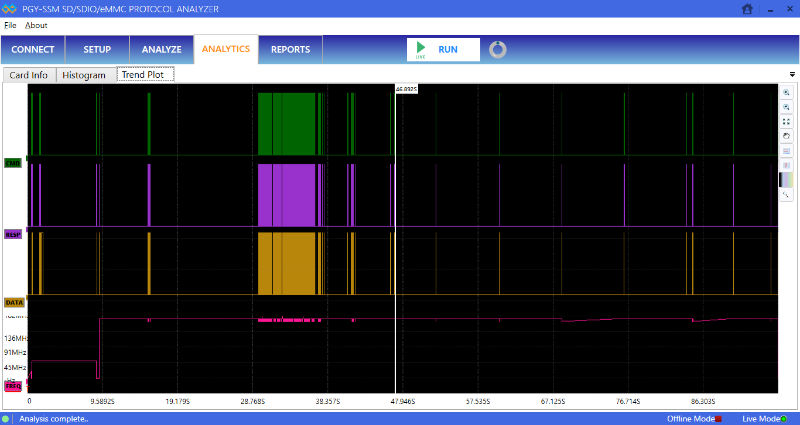

A) Die Analysefunktionen bieten schnell einen Einblick in die Protokollaktivitäten, ohne die gesamte Protokollaktivität durchlaufen zu müssen. Die Analyse-Darstellung ist eine Vogelperspektive auf die Protokollaktivitäten für die erfassten Langzeitdaten. Es reduziert die Analysezeit durch die Anzeige der Plot Command; Response, Daten und Betriebsfrequenz der erfassten Daten. Der Benutzer kann nach einem bestimmten Befehl oder einer bestimmten Antwort im Plot suchen.

Karten-/Geräteinformationen

B) Karten-/Geräteinformationen ermöglichen die Dekodierung des Registerarguments des Gerätes. Der Anwender muss nun nicht mehr jeden Registerwert manuell dekodieren.

Mindestanforderungen Computer

Microsoft Windows® 8, Windows 7, 16GB RAM; Speicher mit mindestens 50 GB Festplattenspeicher für die Speicherung der erfassten Daten. Anzeige mit einer Auflösung von mindestens 1024x768.

Garantie

Für Hardware und Software gilt eine Garantie von einem Jahr. Sonden sind drei Monate Garantie für alle Herstellungsfehler abgedeckt

Technische Daten

| Spezifikation |  |

|---|---|

| Unterstützte Schnittstellen | SD3.0 (UHS-I), SDIO4.0 und eMMC 4.41/4.51/5.0/5.1 Spezifikation |

| Protokoll Dekodierungsbefehle | Command, Response, CRC, Data, Boot Data, Arguments, Device registers |

| Datendekodierung | 1 bit, 4 bit, 8 bit SDR or 4,8 bit DDR |

| Protokoll Tests | Protokoll Integrität, CRC Fehler, Timing values, Data CRC Fehler, Reserved commands |

| Betriebsspannungspegel | 1.8V, 3.3V |

| Speicherfähigkeit | Kontinuierliches Streaming der Protokollaktivitäten bis zu 30 GB oder 4 bis 5 Stunden Aufzeichnungsdauer |

| Aufnahmemodus | Manuelles Starten/Stoppen, Zeitabhängig |

| Aufnahmezeit | 1 Sekunde bis 5 Stunden |

| Trigger on bei | Command, Response, CRC errors, Sequential trigger |

| Trigger Aktionen | Datenerfassung und/oder Trigger Out Signal |

| Signaleingang | Digitaler Signaleingang zur Markierung der Aktivitäten in der Protokollaktivität |

| Host-Computer Schnittstellen | USB3.0 oder GbE |

| Mindestanforderungen an die Host-Maschine | Microsoft Windows® 8, Windows 7, 16GB RAM; Speicherplatz mit mindestens 50 GB Festplattenspeicher für die Speicherung der erfassten Daten. Display mit einer Auflösung von mindestens 1024x768 Pixel |