Produktkonfiguration

Beschreibung

Erweiterte Protokollerfassung und -analyse für PCIe 5.0 Designs

Der PCIe 5.0 Protocol Analyzer wurde für das Design, die Validierung und das Debugging von PCI Express-basierten Systemen entwickelt, die mit PCIe Gen5-Datenraten arbeiten. Der Analyzer unterstützt Analysen bei Geschwindigkeiten von bis zu 32 GT/s und ermöglicht es Ingenieuren, den PCIe-Hochgeschwindigkeitsverkehr präzise zu erfassen, zu dekodieren und Fehler zu beheben. Durch den Einsatz von leistungsstarken Interposern zwischen dem Root Complex und dem Endpunkt (Device Under Test) kannst du umfassende Protokolldaten aufzeichnen und die Markteinführung deiner PCIe 5.0-Produkte beschleunigen.

Eigenschaften PCIe Gen5 Protocol Analyzer

Unterstützt die Dekodierung und Analyse von PCIe Gen1-, Gen2-, Gen3-, Gen4- und PCIe 5.0-Protokollen über x4- und x8-Lane-Breiten.

Ermöglicht die Analyse von PCI Express-Bussen mit vier und acht Lanes für die Geschwindigkeiten Gen1 bis Gen5.

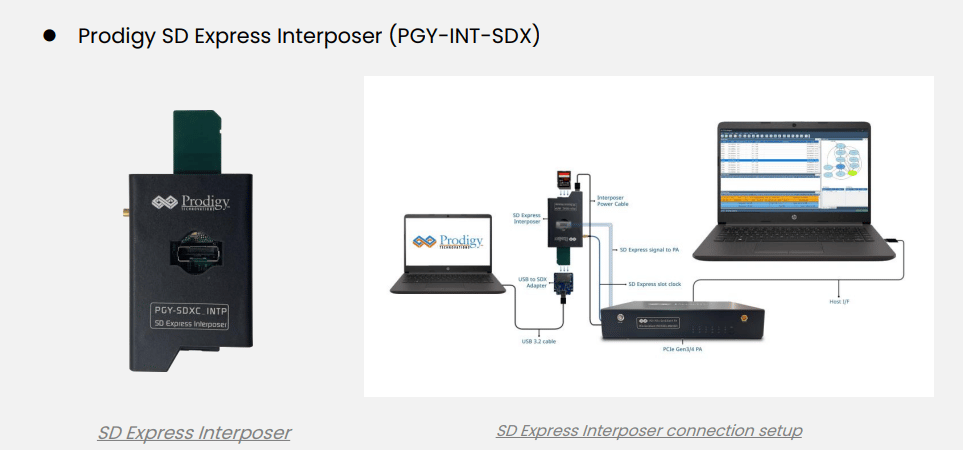

Wird standardmäßig mit M.2-, U.2-, CEM-, E1.S- und SD-Express-Interposern geliefert, die für den Betrieb bis PCIe Gen5 (32 GT/s) validiert sind.

Bietet umfassende NVMe-Protokolldekodierfunktionen für PCIe-basierte Speicheranwendungen.

Optionale Lötkolbenspitzen für vier Lanes, die PCIe-Geschwindigkeiten bis zu Gen3 (8 GT/s) unterstützen.

Dekodiert TS1-, TS2-, TLP- und DLLP-Pakete und bietet damit vollständige Transparenz auf der Protokollschicht.

Protokoll-Paketfilterung auf Hardware-Ebene für TS1-, TS2- und IDLE-Sequenzen zur Optimierung der Erfassungseffizienz.

Softwarebasierte Such-, Filter-In- und Filter-Out-Funktionen für eine schnellere Isolierung und Analyse des Datenverkehrs.

Hardware-Protokoll-basierte Trigger-Mechanismen auf der Grundlage von TS1-, TS2-, TLP- und DLLP-Paketinhalten.

Unterstützt eine fortschrittliche mehrstufige Wenn-Dann-Else-Trigger-Logik zur Erkennung komplexer Ereignisse.

Standardmäßig 16 GB Erfassungspuffer, erweiterbar auf bis zu 64 GB kombiniert für TX und RX.

Bietet detaillierte Ansichten auf Feldebene für jedes TLP und DLLP und ermöglicht so eine präzise Paketprüfung.

Integrierte LTSSM-Analyse zur Überwachung von PCIe-Link-Training und Zustandsübergängen.

Segmentierte Speicherarchitektur, so dass jedes Erfassungssegment mit einer anderen Triggerbedingung arbeiten kann.

Bietet ein Trigger-Out-Signal zur Synchronisierung und zum Triggern externer Instrumente wie z. B. Oszilloskope.

Anschluss an das Hostsystem über eine USB 3.0-Schnittstelle für Hochgeschwindigkeitsdatenübertragung.

Ermöglicht den Export von dekodierten Protokolldaten im .txt-Format für die weitere Offline-Analyse.

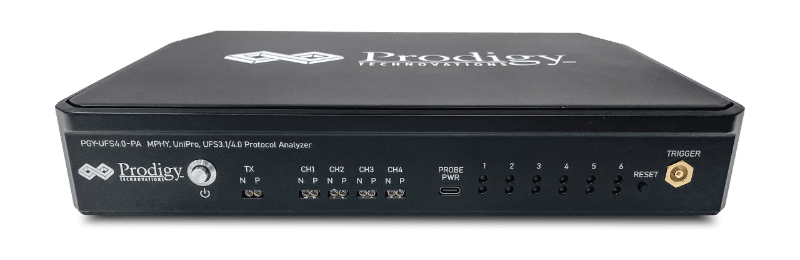

Durch sein leichtes und tragbares Design eignet sich der Protokollanalysator für Tests vor Ort und im Feld.

Vor Ort aufrüstbare Plattform, die einfache Wartung und Firmware-Updates aus der Ferne ermöglicht, um auf die neuesten Funktionen zuzugreifen.

PCIe Protokoll Software

Technische Daten

| Spezifikation |  |

|---|---|

Data Rates Supported | PCIe Gen1, Gen2, Gen 3, Gen 4, Gen5 |

Link Width | Four/Eight lanes (Four/Eight TX and Four/Eight RX). |

Probes | M.2 Interposer (Standard), Optional orderable CEM, U.2, E1.S, SD Express Interposers Solder Down Active Probes for speeds up to PCIe Gen3. (Optional) |

Protocol Decode | TS1, TS2, TLP, DLLP, SDS, IDLE, EIOS, EIEOS, FTS, SKP, NVME, Decoding of Configuration register |

Trace Capture Size | Supports Continuous streaming of Protocol data to Host computer SSD/HDD and Post Capture up to buffer size. |

Trigger | Based on TS1, TS2, TLP, DLLP. |

Connectors | Interposer Interface and Trigger in/out signal |

Interface for Host Computer | USB 3.0 |

Host Computer Requirements | Processor: Intel i7 10th Generation or better (Equivalent) Operating System: Windows 8.0/8.1/10/11 64bit OS. RAM: minimum 16GB but the product would give a faster response for 32GB/64GB/more. Storage: 256GB SSD or more (minimum storage capacity of 1GB should be available in the hard disk drive. User can use more storage based on trace storage requirement.) Display resolution: 1024X768. |

Dimension (WxHxD) | (W x H x D) (20.5X5X25) cms. (Tentative) |

Weight | Approx. 6 kg |

Power Requirement | 12V, 6A DC Power Supply (AC/DC Supplied along with Analyzer). |

.jpg)

.jpg)

.jpg)