Beschreibung

Die MIPI UniPro-Protokolldekodierungssoftware bietet Protokolldekodierung gemäß der MIPI UniPro-Spezifikation. Die PGY-MIPI UniPro Protocol Decode Software läuft im Tektronix Oszilloskop und liefert auf Knopfdruck Messungen zur Protokolldekodierung. So können sie schnell prüfen, ob die MIPI UniPro-Spezifikation eingehalten wird, und sind flexibel bei der Fehleranalyse. Darüber hinaus können sie auch den Command und die Response von MIPI UniPro dekodieren, um die Kommunikation zu debuggen. PGY-MIPI UniPro nutzt die Vorteile der digitalen Kanäle von MSO und bietet die Dekodierung von MIPI UniPro-Datenleitungen.

Features ONFI Protokoll Software

- UniPro- und LLI-Protokolldecoder ermöglichen ein schnelleres Debuggen von Protokollen auf Systemebene

- Entspricht der UniPro-Protokollspezifikation Version 1.6 und dem LLI-Protokoll Version 1.0

- Entspricht der UFS-Protokoll-Spezifikation Version 2.0

- Unterstützt NRZ- (Non-Return-to-Zero) und PWM- (Pulse Width Modulation) Signalisierungsschemata

- Konfigurierbare gleichzeitige Dekodierung des Protokolls für vier Fahrspuren hilft bei der Korrelation der Ereignisse zwischen den Fahrspuren

- Autolink der dekodierten Daten von der Listentabelle zur Oszilloskop-Wellenform für einfaches Protokoll-Debugging auf PHY-Ebene

- Leistungsstarke UniPRO/LLI-Protokoll-bewusste Triggerfunktionen unter Verwendung der seriellen Triggerfunktion der Oszilloskope der Option ST6G

- Triggerung unterstützt PWM, NRZ und 8b/10B kodierte Datenschemata

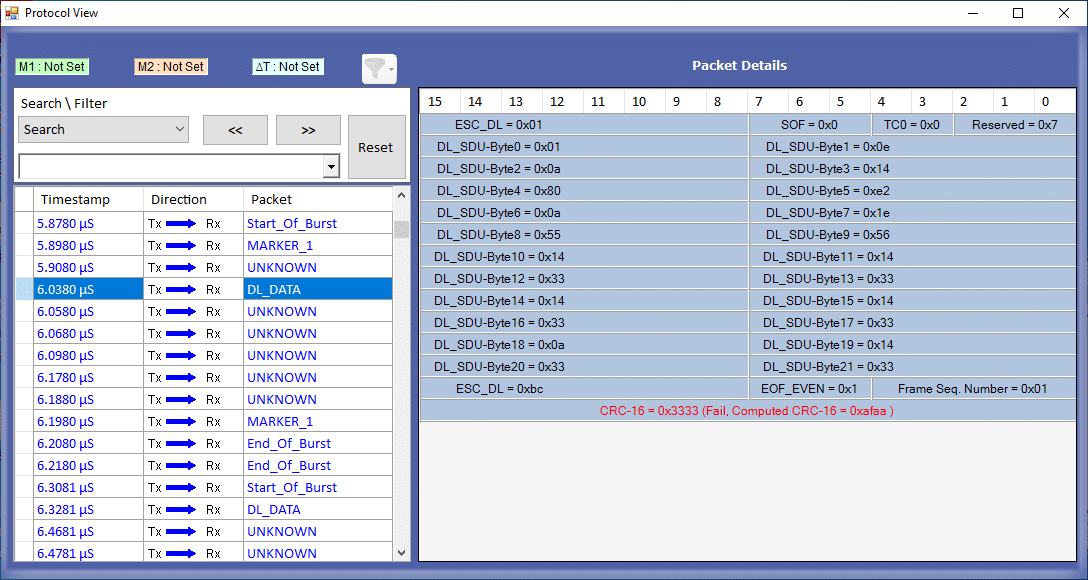

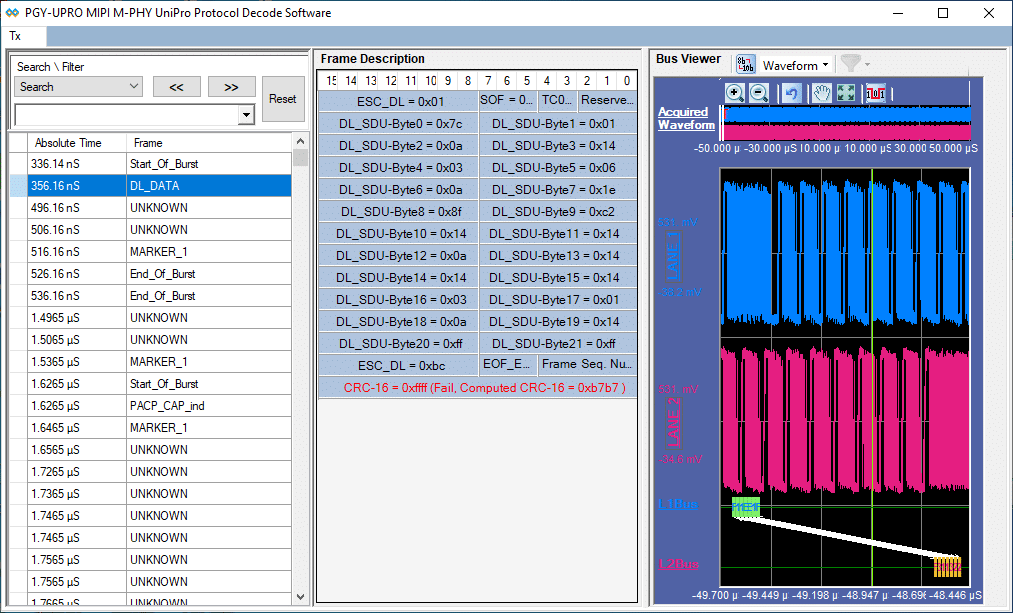

- Die Detailansicht bietet eine umfassende Korrelation von Protokoll- und Bitübertragungsschichtdaten

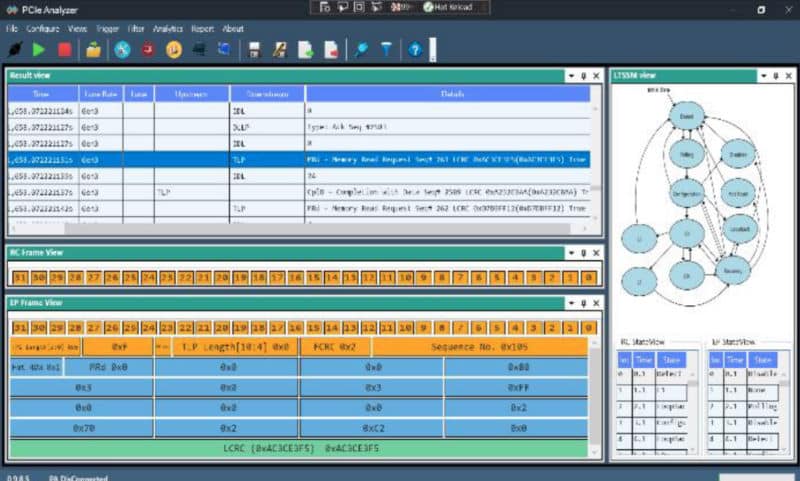

- Frame-Listing und Frame-Beschreibung liefern umfassende Informationen zur Protokollschicht

- Jeder Frame wird gemäß den UniPro- und LLI-Standardspezifikationen detailliert angezeigt

- Automatische CRC-Berechnung zur Überwachung von CRC-Fehlern in den Protokollpaketen

- Markierungen ermöglichen die Zeitmessung zwischen Nachrichten in verschiedenen Lanes

- Die Software identifiziert automatisch das Signalisierungsschema und das Getriebe für eine problemlose Protokollanalyse

- Busdiagramm-Funktionen wie Zoom, Un-Zoom, Pan, Fit to Screen und Synchronisationsfunktionen ermöglichen eine einfache Datenanalyse

- Unterstützt Oszilloskop-Live-Kanäle und Tektronix .wfm-Wellenformdateien

- Generiert umfassende und anpassbare Berichte

- Möglichkeit, die Protokolldetails in txt- und CSV-Dateiformate zu exportieren

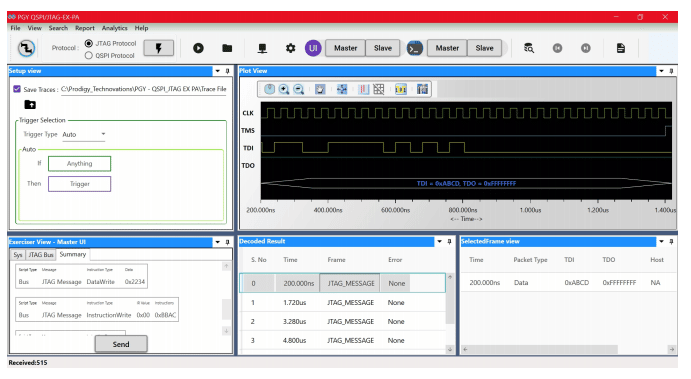

Protokoll Ansicht

Die PGY-UPRO/LLI/UFS Protocol Decode Software bietet eine umfassende Protokolldecodierung für MIPI-MPHY-UniPRO-, LLI- und UFS-Protokollstandards. Die Software bietet Hardware-basierte UniPRO/UFS-Protokoll-Trigger in Echtzeit für PWM-, NRZ- und 8B/10B-Datentypen. Jetzt können Entwicklungs- und Testingenieure mit der PGY-UPro/LLI/UFS-Software automatisch eine genaue und zuverlässige Dekodierung von Multi-Lane-UniPRO/LLI/UFS vornehmen, indem sie Daten verwenden, die mit Oszilloskopen der Serien DPO/DSA/MSO70000 von Tektronix erfasst wurden, um den Entwicklungs- und Testzyklus zu verkürzen.

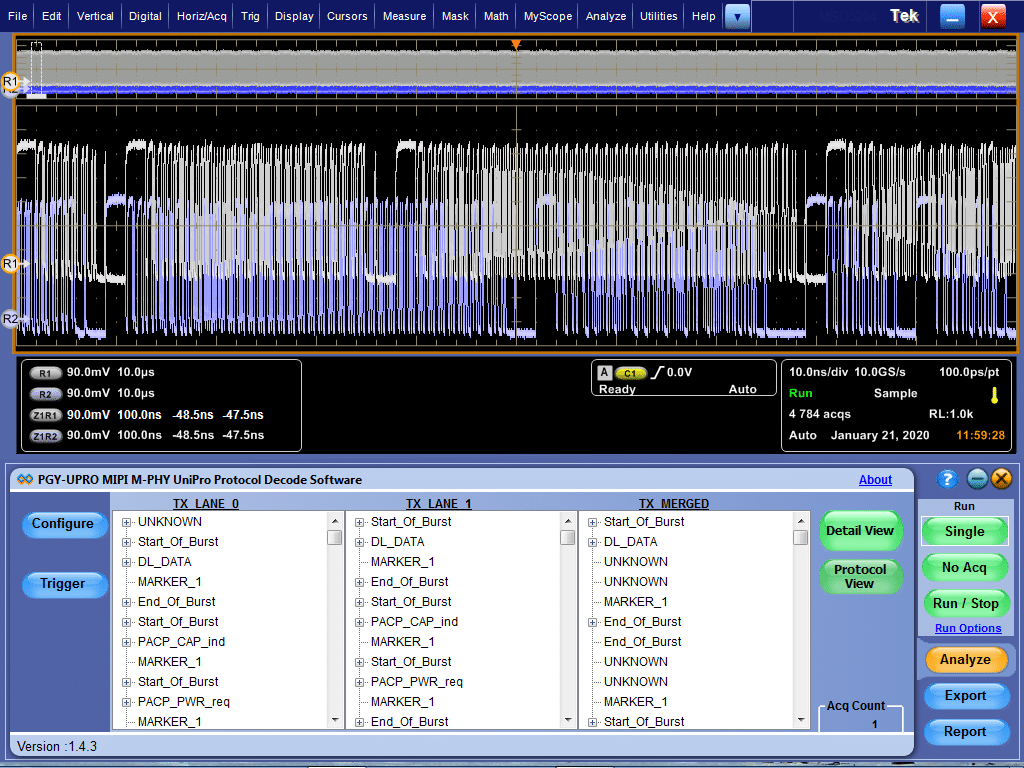

Nahtlose Integration mit Tektronix Oszilloskop

Der PGY-UPRO/LLI/UFS läuft innerhalb der Tektronix-Oszilloskope, dekodiert Protokolle und zeigt die dekodierten Daten mehrerer Lanes an. Diese Software verknüpft die dekodierten Daten mit dem elektrischen Signal auf der Oszilloskopanzeige. UniPRO/LLI-Protokoll-basierte Trigger können mit den integrierten seriellen Hochgeschwindigkeits-Triggerfunktionen der Tektronix-Oszilloskope eingerichtet werden.

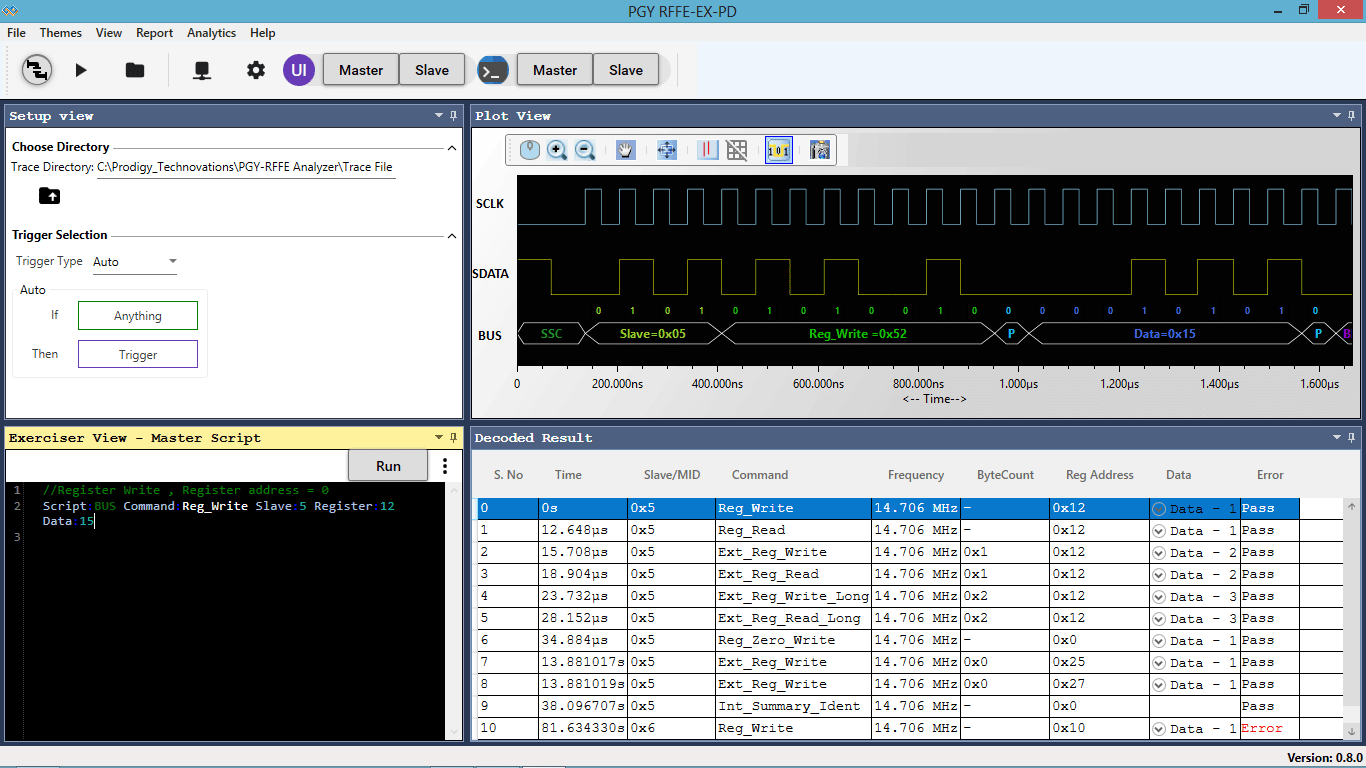

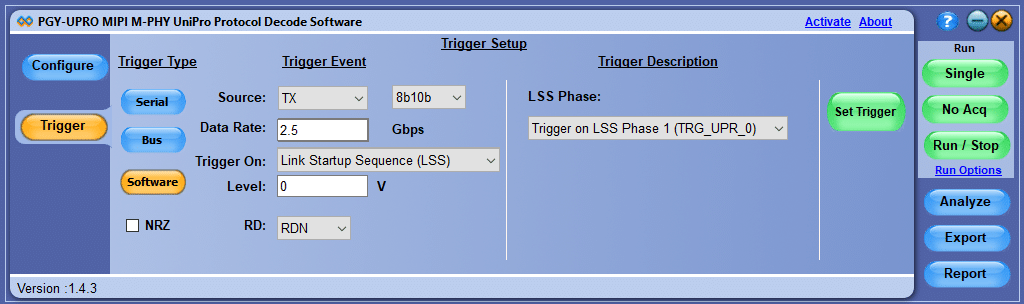

UniPRO-Protokoll Aware Trigger

Die PGY-UPRO/LLI/UFS-Software bietet protokollabhängige Triggerbedingungen wie die Startsequenz der Verbindung, den Inhalt der PHY-Adapterschicht und den Inhalt der Datenübertragungsschicht. Die einzigartigen Fähigkeiten dieser Software ermöglichen Trigger-Datentypen wie PWM, NRZ oder 8B/10B serielle Daten des Protokolls. PGY-UPRO unterstützt die folgenden Protocol Aware Trigger-Funktionen.

PGY-UFS Modul

PGY-UFS ist ein optionales Modul für die PGY-UPRO-Software, das die Protokolldekodierung von UFS-Inhalten im Data-Link-Layer-Paket ermöglicht. Die PGY-UFS-Software extrahiert die im Data-Link-Paket enthaltenen UFS-Informationen und zeigt sie in der UFS Protocol Information Unit (UPIU) an. PGY-UFS hat die Flexibilität, nur den UFS-Protokollinhalt oder UFS- und UniPRO-Daten für einfache Fehlersuche anzuzeigen.

Unterstützte Tektronix Oszilloskope

- DPO 70000

- MSO 70000

- DSA 70000

| Trigger Event | Trigger Content |

|---|---|

| Link Start up Sequence (LSS) | Trigger on LSS Phase 1 (TRG_UPR_0) Trigger on LSS Phase 2 (TRG_UPR_1) Trigger on LSS Phase 3 (TRG_UPR_2) |

| PHY Adapter layer Content | PACP_PWR_req PACP_PWR_cnf PACP_cap_ind PACP_EPR_ind PACP_TEST_MODE_req PACP_GET_req PACP_GET_cnf PACP_SET_req PACP_SET_cnf PACP_Test_Data |

| Data Link layer Content | Data_SOF Data_COF AFC (Acknowledgement) NAC (No Acknowledgement) |

.jpg)

.jpg)

.jpg)