Prodigy eSPI Elektrische Validierung und Protokolldekodierungssoftware für Tektronix Oszilloskop

Beschreibung

Die Software zur elektrischen Validierung und Protokolldekodierung von eSPI bietet Konformitätsprüfungen für elektrische Messungen und Protokolldekodierung gemäß der eSPI-Spezifikation. Die PGY-eSPI-Software für die elektrische Validierung und Protokolldekodierung läuft auf dem Tektronix-Oszilloskop und bietet elektrische Messungen und Protokolldekodierung auf Knopfdruck. Dies ermöglicht Ingenieuren eine schnelle Überprüfung der eSPI-Konformität und Flexibilität bei der Fehlersuche. Darüber hinaus kann der Ingenieur den Befehl und die Antwort von eSPI dekodieren, um die Kommunikation zu debuggen. PGY-eSPI nutzt die Vorteile der digitalen Kanäle von MSO und ermöglicht die Dekodierung von eSPI-Datenleitungen.

Features eSPI Software

- Elektrische Messungen und Protokolldekodierung für Singlemode-, Dualmode- und Quadmode-Analysen mit analogen Kanälen

- Protokolldekodierung im Single-, Dual- und Quad-Mode mit digitalen Kanälen

- Anpassbare Referenz- und Hystereseauswahl für alle Signale

- Anpassbare Grenzwerteinstellung für Pass/Fail-Validierung für alle Messungen

- Anpassbare Grenzwerte basierend auf verschiedenen Datenraten

- Möglichkeit zur Speicherung der eSPI-Protokolldaten und der elektrischen Daten im CSV- und txt-Format

- Erstellung von Berichten

- Offline-Analyse von .wfm- und .csv-Dateien (digital)

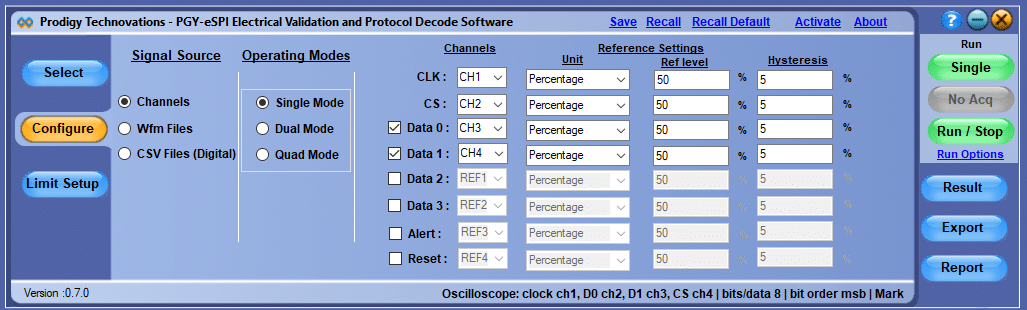

Konfigurationspanel

Das Konfigurationsfeld dient zur Auswahl der Signalquelle und des anfänglichen Betriebsmodus.

Analoge oder digitale Live-Kanäle des Oszilloskops können für die Erfassung und Analyse des Signals verwendet werden. Die Software dekodiert die Wellenform und zeigt sowohl die Protokolldaten als auch die elektrischen Messungen im Falle von analogen Signalen und Protokolldaten im Falle von digitalen Signalen an.

Die anfängliche Betriebsart des Busses (einfach/zweifach/vierfach) muss ausgewählt werden, damit die Software das Signal entsprechend dekodieren kann. Dies ist nur der Anfang der Analyse. Auf der Grundlage der bei der Dekodierung erhaltenen Registerwerte aktualisiert die Software die Betriebsart und dekodiert automatisch die eSPI-Operationen.

Zur Charakterisierung und Validierung von eSPI-Signalen bietet die PGY-eSPI-Software ein grafisches Messreferenzpegel-Setup zur Einstellung des Messreferenzpegels von eSPI-Signalen.

Unterstützte elektrische eSPI-Messungen

- Clock Frequency

- Clock High Time

- Clock Low Time

- Chip Select Setup Time

- Chip Select Hold Time

- Chip Select Deassert Time

- Data In Setup Time

- Data In Hold Time

- Output Data Valid Time

- Output Data Hold Time

- Output Disable Time after Chip Select Deassert

- Output Disable Time during Turn Around

- Chip Select Assert to Data1 or Alert Tristated

- Chip Select Deassert to Data1 or Alert Assert

- eSPI Reset Deassert to First Transaction

- Initial Bus Frequency upon Reset Deassert

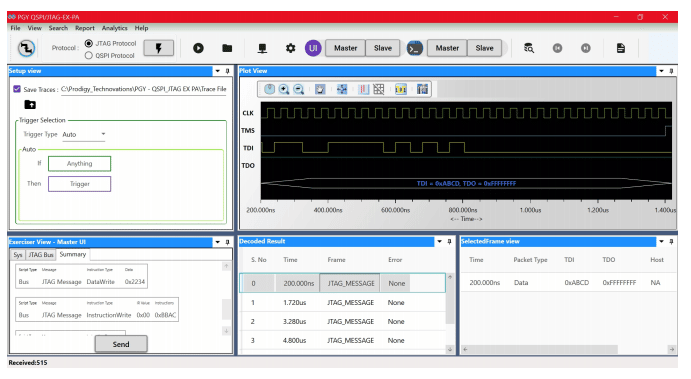

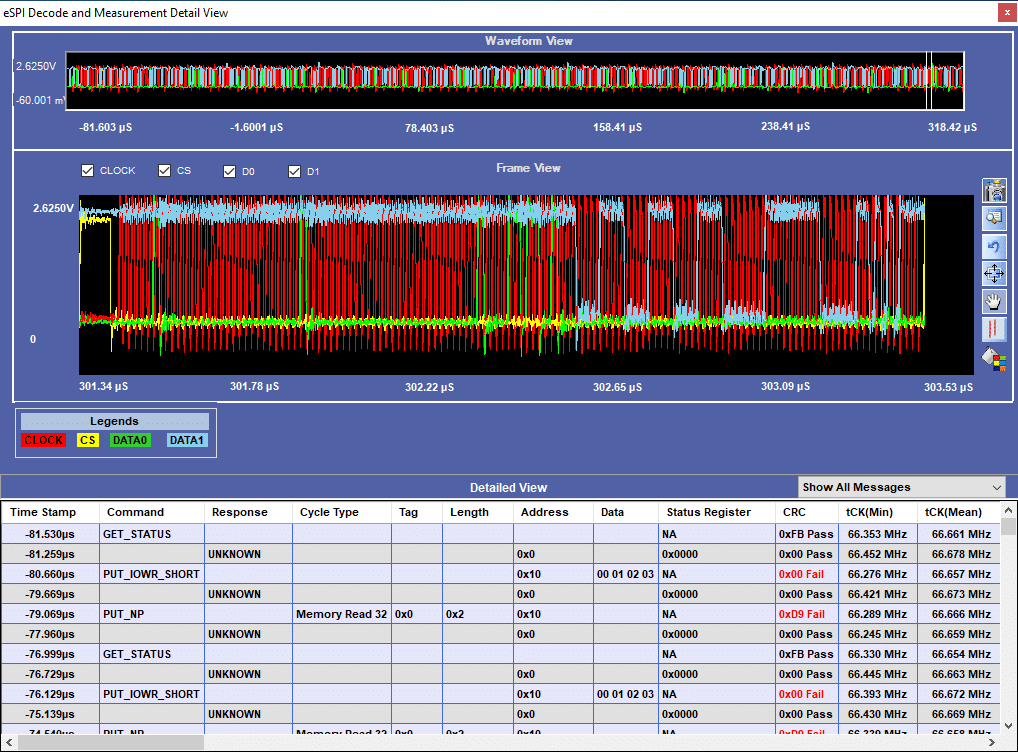

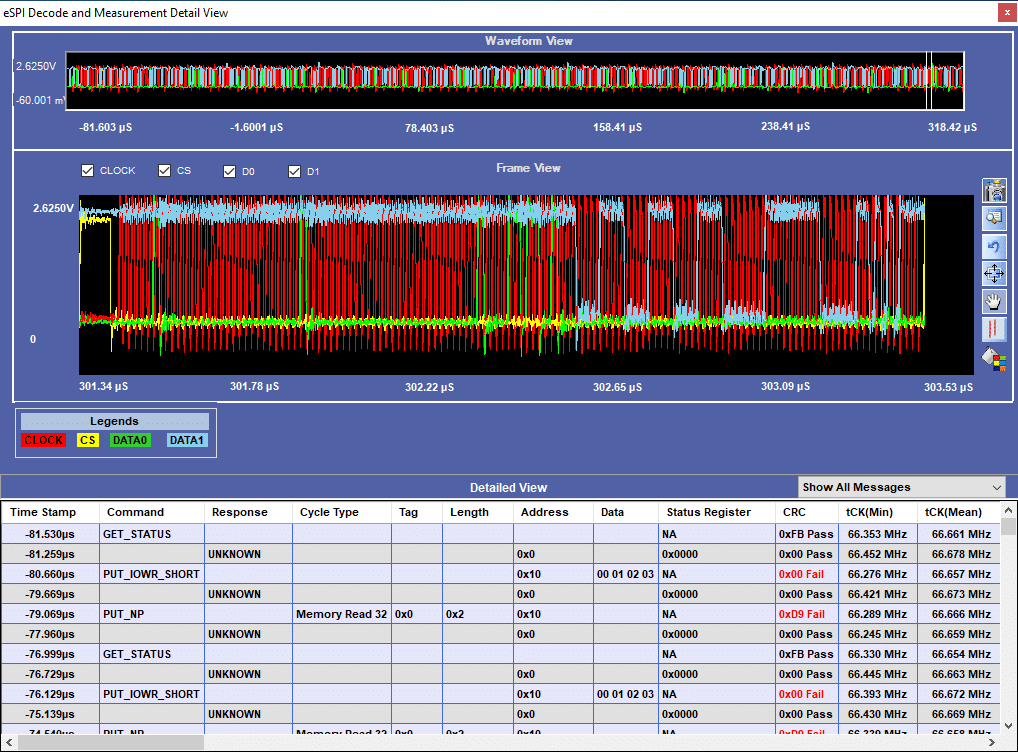

Detail Ansicht

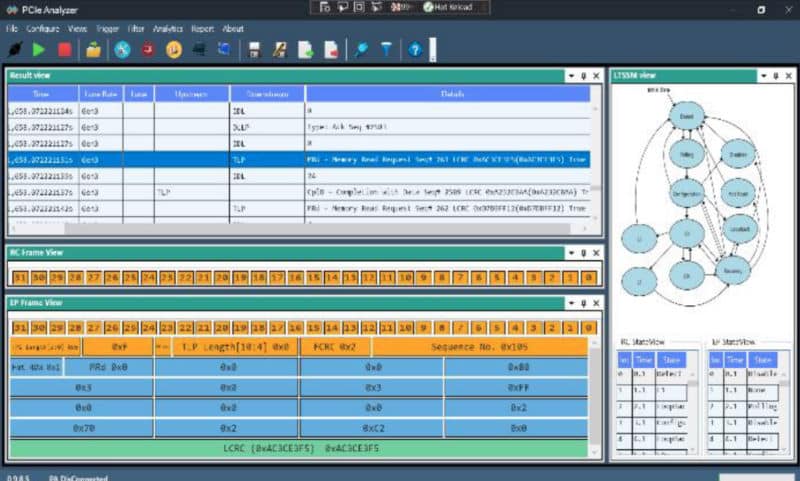

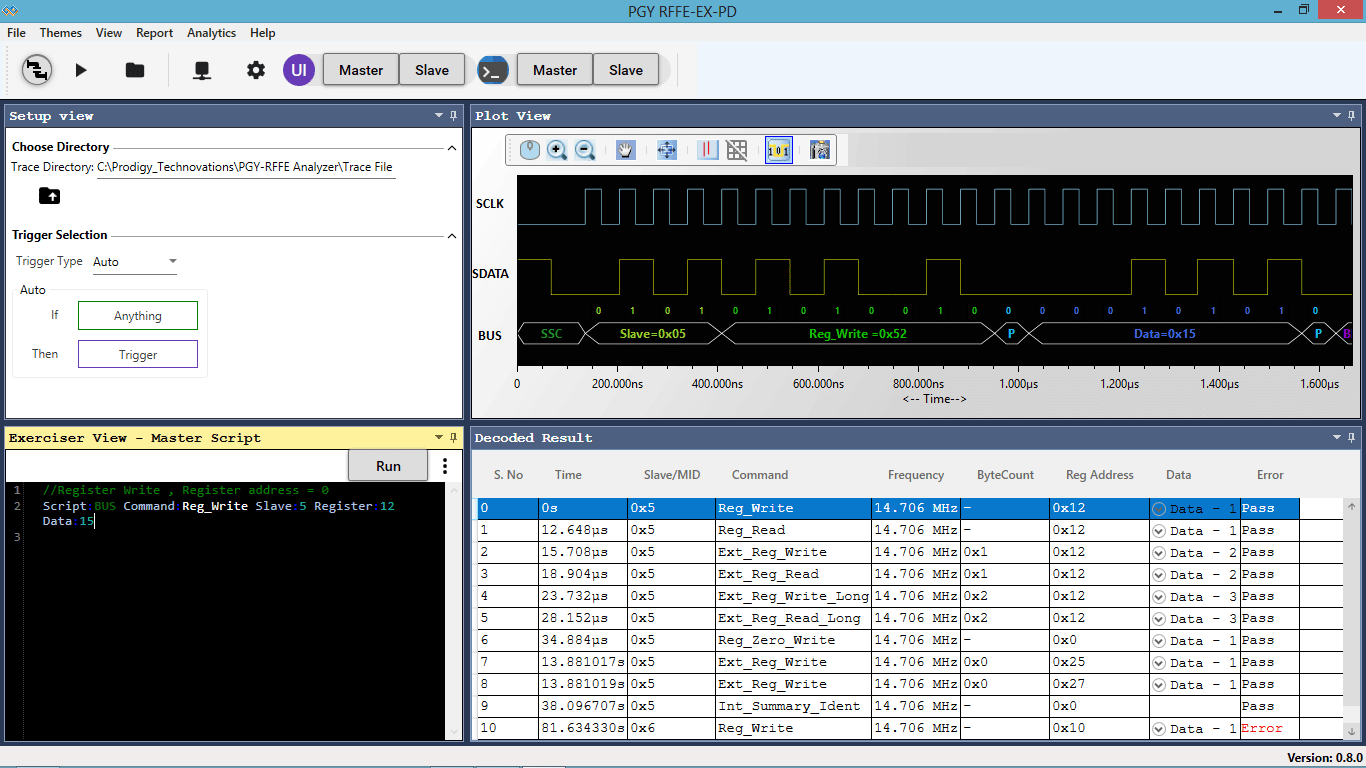

Sobald ein elektrischer Fehler oder ein Protokollproblem vorliegt, müssen spezifische Protokollpakete gefunden werden, um die Designprobleme zu beheben. In der Detailansicht wird die erfasste Wellenform aufgezeichnet. Die Wellenformdarstellung ist mit dem Paket verknüpft, das auf dem Raster angezeigt wird. Die Darstellung enthält verschiedene Funktionen wie Zoom, Pan und Cursor. Durch die Verknüpfung spezifischer Protokollpakete mit den elektrischen Wellenformen können Ingenieure die Ursache der Probleme schnell ausfindig machen.

Unterstützte Tektronix Oszilloskope

- DPO 70000

- MSO 70000

- DSA 70000

.jpg)

.jpg)

.jpg)